# Securing Operating Systems Through Utility Virtual Machines

#### A Thesis

### Submitted to the Faculty

in partial fulfillment of the requirements for the

degree of

Doctor of Philosophy

by

Robert Denz

Thayer School of Engineering

Dartmouth College

Hanover, New Hampshire

June 2017

|       | •   | •     | $\sim$ | •      |

|-------|-----|-------|--------|--------|

| Hvam  | 111 | 1na   | Com    | mittee |

| Lanin | ш   | 11112 | COIL   | mittee |

| Chairman |                          |

|----------|--------------------------|

|          | Stephen Taylor, Ph.D.    |

| Member_  |                          |

|          | George Cybenko, Ph.D.    |

| Member   |                          |

|          | Eugene Santos, Jr. Ph.D. |

| Member   |                          |

|          | Ryan Durante, Ph.D.      |

|          |                          |

F. Jon Kull

Dean of Graduate Studies

#### **Abstract**

The advent of hypervisors revolutionized the computing industry in terms of malware prevention and detection, secure virtual machine managers, and cloud resilience. However, this has resulted in a disjointed response to handling known threats rather than preventing unknown zero-day threats. This thesis introduces a new paradigm to cloud computing – utility virtual machines – that directly leverages virtualization hardware for protection and eliminates often accepted roles of the operating system kernel. This represents a break from prevailing practices and serves to establish a hardware root of trust for system operation.

#### Acknowledgments

I would like to thank my adviser Dr. Stephen Taylor for his valued support while in graduate school. He provided me with the opportunity to delve deep into the fields of virtualization and symmetric multiprocessing. Giving me the time and resources to develop a far deeper understanding of computing systems and an appreciation for the academic process.

As Rome wasn't built in a day or by a single individual, I would like to thank my research group Scott Brookes, Martin Osterloh, Stephen Kuhn, Morgon Kanter, Jason Dahlstrom, and Colin Nichols, who without them, much of the development would still be on going. Through our combined efforts we have built a truly modern system, which has provided a wealth of novel research topics. Those outside of the research group, Jacob Russell, who as a coworker, friend, and roommate has always provided a keen perspective on the work our group does and Karen Thurston who has been invaluable in helping me balance the logistical details of a Ph.D.

Specifically, I would like to thank my parents Michael and Mary Denz who have supported me throughout academia, career, and academia again. You have been role models throughout my life and always provided me the wisdom needed to make the right choice. Also deserving of thanks is my sister, Brittany Denz, an integral part of my family support system.

My fiancée Emily, who has provided all means of support to me over the years, from home cooked meals, to fun family getaways, as well as allowing me to turn our dining room into my makeshift office to finalize the remainder of my thesis. You have gone above and beyond in your support of me on this journey.

Lastly, every one who has listened to me spend days complaining about a random bug in my code.

This research is supported by the Defense Advanced Research Projects Agency as part of the MRC program under contract FA8750-11-2-0257. The U.S. Government is authorized to reproduce and distribute reprints for Governmental purposes notwithstanding any copyright notation thereon. The views and conclusions contained herein are those of the authors and should not be interpreted as necessarily representing the official policies or endorsements, either expressed or implied, of the Defense Advanced Research Projects Agency (DARPA) or the U.S. Government.

# Table of Contents

| Abstract                              | ii   |

|---------------------------------------|------|

| Acknowledgments                       | iii  |

| Table of Contents                     | V    |

| List of Tables:                       | ix   |

| List of Figures:                      | X    |

| List of Acronyms                      | xiii |

| Chapter 1 – Introduction              | 1    |

| 1. 1 Background & Motivation          | 2    |

| 1.2 Approach                          | 8    |

| 1.3 Performance Metrics               | 13   |

| 1.4 Contributions                     | 14   |

| 1.5 Thesis Organization               | 16   |

| Chapter 2 – Related Work              | 18   |

| 2.1 Threat Model                      | 20   |

| 2.2 Malware Detection and Prevention  | 22   |

| 2.3 Secure Virtual Machine Managers   | 27   |

| 2.4 Cloud Resilience                  | 32   |

| 2.5 Comparative Analysis              | 33   |

| 2.6 Related Fields of Work            | 37   |

| 2.7 Summary                           | 37   |

| Chapter 3 – Symmetric Multiprocessing | 39   |

| 3.1 Introduction                      | 39   |

| 3.1.1 Basic Concepts                  | 43   |

| 3.1.2 Overview                                                       | 50  |

|----------------------------------------------------------------------|-----|

| 3.2 Stage-One Bootloader                                             | 53  |

| 3.2.1 CPU Configurations                                             | 55  |

| 3.2.2 Physical Memory Profiling                                      | 57  |

| 3.2.3 Initial Page Table Creation                                    | 59  |

| 3.3 Stage-Two Bootloader and Memory Manager                          | 63  |

| 3.3.1 An Array of Structures                                         | 64  |

| 3.3.2 Growing the Initial Page Tables Through Recursion              | 66  |

| 3.3.3 Mapping and Populating the Frame Array                         | 70  |

| 3.4 Hypervisor                                                       | 74  |

| 3.4.1 Utilizing the Application Processor Cores                      | 75  |

| 3.4.2 Finding the Application Processor Cores                        | 76  |

| 3.4.2.1 Advanced Configuration Power Interface Table                 | 77  |

| 3.4.3 SMP configuration for the Bootstrap Processor                  | 81  |

| 3.4.3.1 Enabling the APIC                                            | 81  |

| 3.4.3.2 Configuring the APIC Timer                                   | 83  |

| 3.4.3.3 Configuring the I/O APIC                                     | 86  |

| 3.4.4 Booting the Application Cores                                  | 90  |

| 3.4.5 Hypervisor Modifications to Support APIC Access Virtualization | 94  |

| 3.4.6 Enabling APIC Access Virtualization                            | 97  |

| 3.4.6.1 APIC Access Virtualization Exit Handling                     | 98  |

| 3.4.6.2 Joining Cores to a Running Guest                             | 100 |

| 3.5 Micro-Kernel SMP Scheduling Considerations                       | 102 |

| 3.5.1 Locking and Transitions                                        | 103 |

| 3.5.2 User & Idle Process Scheduling                                 | 105 |

| 3.6 Benchmarks and Analysis                                        | 106 |

|--------------------------------------------------------------------|-----|

| 3.7 Summary                                                        | 109 |

| Chapter 4 – Utility Virtual Machines                               | 110 |

| 4.1 Building the first UVM                                         | 111 |

| 4.2 Extending Message Passing to the Hypervisor                    | 115 |

| 4.3 Pairing Two UVMs Together                                      | 121 |

| 4.4 Benchmarking and Analysis                                      | 124 |

| 4.5 Summary                                                        | 126 |

| Chapter 5 – A Further Abstraction: The Network UVM                 | 128 |

| 5.1 Network Utility Virtual Machine Helper Daemon (NUVMHD)         | 129 |

| 5.2 Implementing the Network UVM                                   | 131 |

| 5.3 Benchmarking and Analysis                                      | 133 |

| 5.4 Summary                                                        | 135 |

| Chapter 6 – Heat Diffusion Scheduling                              | 136 |

| 6.1 Implementing diffusion                                         | 140 |

| 6.2 Benchmarks and Analysis                                        | 146 |

| 6.3 Summary                                                        | 150 |

| Chapter 7 – Conclusions and Future Work                            | 152 |

| 7.1 Conclusions                                                    | 152 |

| 7.2 Future Work                                                    | 155 |

| Appendix A – Stage One Bootloader Code                             | 157 |

| Appendix B – Register Layouts                                      | 169 |

| APPENDIX C – Macros for paging                                     | 170 |

| Annendix D – Paging Structures & Frame Array Initialization C Code | 171 |

| APPENDIX E – ACPI Structures and APIC Handling Code | . 181 |

|-----------------------------------------------------|-------|

| APPENDIX F – Fields and Values for APIC MMIO        | 186   |

| Appendix G – Time Stamp Counter (TSC) Handling Code | 187   |

| Appendix H – VMEXIT APIC Access Handling Code       | 190   |

| Appendix I – Utility Virtual Machine Queue Code     | 193   |

| Bibliography                                        | . 195 |

# **List of Tables:**

| Table 1 - Comparison Summary of Surveyed Systems | 34  |

|--------------------------------------------------|-----|

| Table 2 - Overhead Cost of Frame Array           | 66  |

| Table 3 - Memory and Processor Benchmarks        | 107 |

| Table 4 - Keyboard/VGA UVM Benchmarks            | 125 |

| Table 5 - Network UVM Benchmarks                 | 133 |

| Table 6 - Scheduler Performance Characterization | 147 |

| Table 7 - Summary of Attack Surface Reduction    | 153 |

# **List of Figures:**

| Figure 1 - Bare-Metal Hypervisor                                      | 3  |

|-----------------------------------------------------------------------|----|

| Figure 2 - Bare-Metal Hypervisor with Utility Virtual Machines        | 7  |

| Figure 3 - Bear System Layout                                         | 10 |

| Figure 4 - Example Security Techniques in the Cloud                   | 19 |

| Figure 5 - Threat Model                                               | 21 |

| Figure 6 – Example Covert channel                                     | 29 |

| Figure 7 - Overview of Steps Required for SMP Enabled System          | 51 |

| Figure 8 - Stage-One Bootloader Pseudo Code                           | 55 |

| Figure 9 – Bios Memory Map Creation Assembly Code                     | 58 |

| Figure 10 - Initial Page Table Creation Assembly Code                 | 60 |

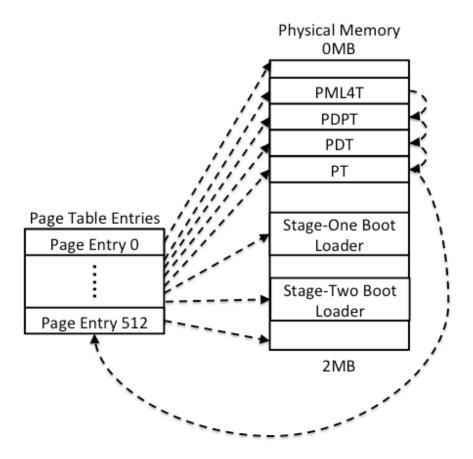

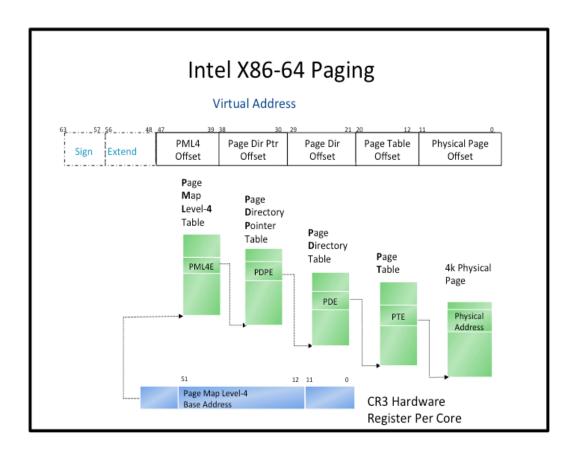

| Figure 11 - Four Level Page Table Layout (Intel Manual)               | 61 |

| Figure 12 - Initial Page Table Memory Layout and Mapping              | 63 |

| Figure 13 - C Frame Array Structure                                   | 65 |

| Figure 14 - X86-64 Virtualization (Intel Manual)                      | 69 |

| Figure 15 - Recursive Pointer Page Table Entry Assembly Code          | 70 |

| Figure 16 - C Bios Interrupt 15 Memory Map Structure                  | 71 |

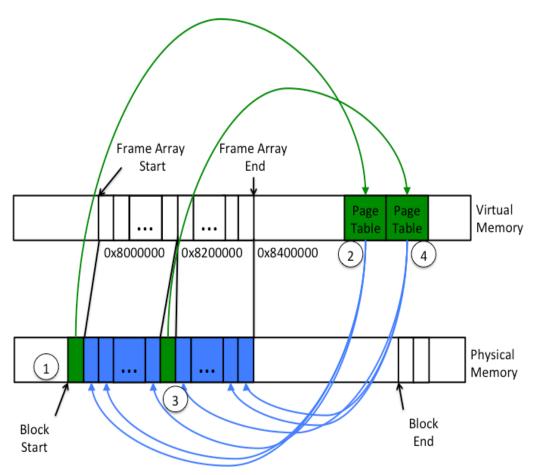

| Figure 17 - Virtual Mapping of the Frame Array via Recursive Pointer  | 72 |

| Figure 18 - Process for Booting Application Cores                     | 76 |

| Figure 19 - Process for Finding and Parsing ACPI Tables               | 77 |

| Figure 20 - Remote System Descriptor Pointer (RSDP) and Search Code   | 78 |

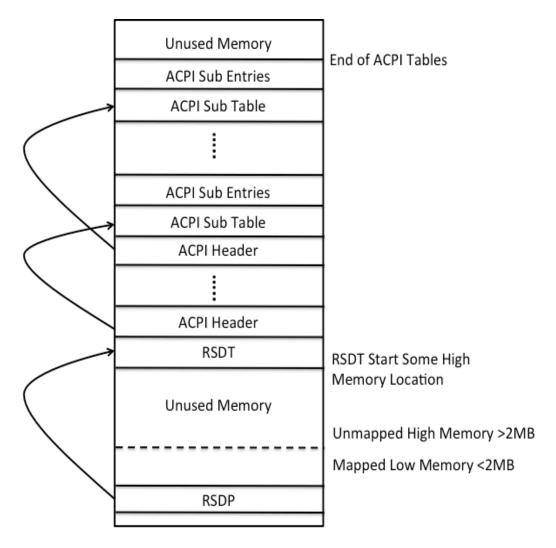

| Figure 21 - ACPI Layout in Memory                                     | 79 |

| Figure 22 - Code to Enable Advanced Programmable Interrupt Controller | 82 |

| Figure 23 - C Code to Program APIC Timer                          | 86  |

|-------------------------------------------------------------------|-----|

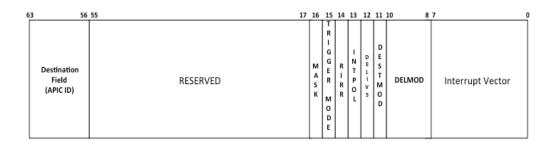

| Figure 24 - I/O APIC Registry Table Entry                         | 87  |

| Figure 25 - C I/O APIC and I/O APIC Read Write Helper Functions   | 88  |

| Figure 26 - C Code to Initialize the I/O APIC                     | 89  |

| Figure 27 - C Code to Enable an I/O APIC Entry                    | 89  |

| Figure 28 – Application Core Trampoline Pseudo Code               | 90  |

| Figure 29 - Process to Start Application (AP) Cores               | 92  |

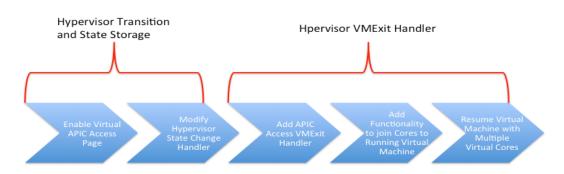

| Figure 30 - Steps to Support SMP Guest Virtual Machines           | 94  |

| Figure 31 - C Structure of Hypervisor Core Specific Local Storage | 96  |

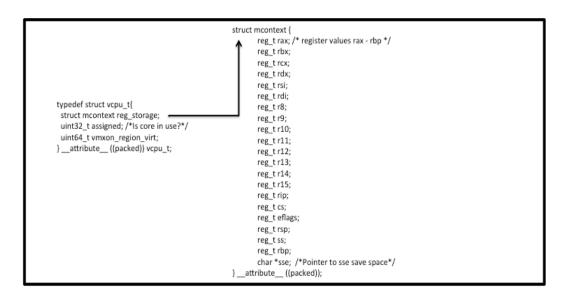

| Figure 32 - VCPU Structure Initialization                         | 97  |

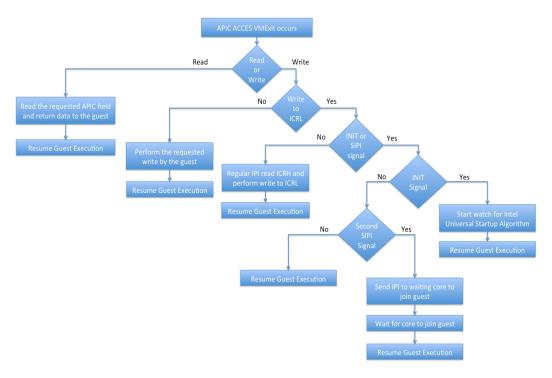

| Figure 33 - Hypervisor APIC VMExit Handling Flow Chart            | 98  |

| Figure 34 - C Structure for Guest Virtual Machine                 | 101 |

| Figure 35 - Function to Join AP to Virtual Machine                | 102 |

| Figure 36 - C Code to Implement Spin-Locking                      | 104 |

| Figure 37 - Assembly Code to Idle a Core                          | 106 |

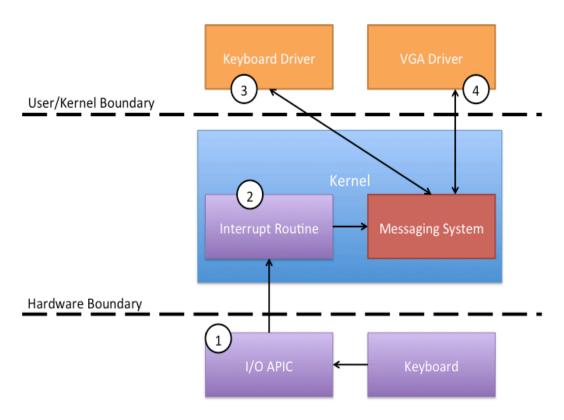

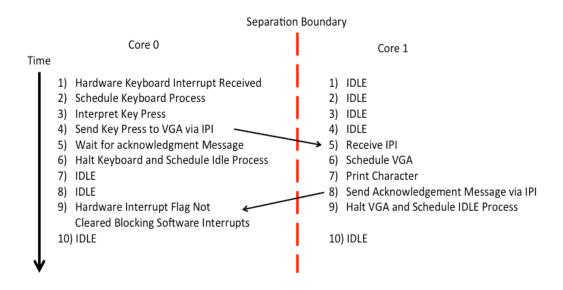

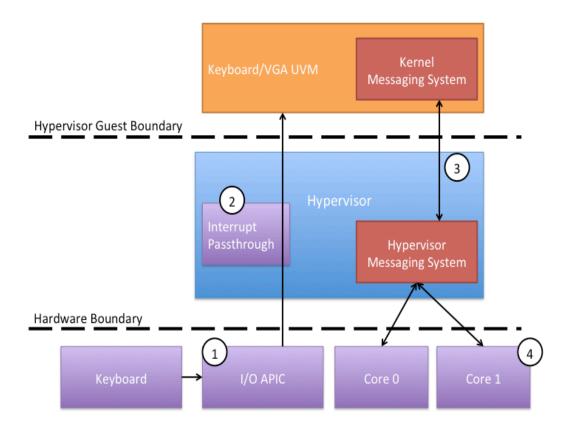

| Figure 38 - Keyboard/VGA UVM Kernel Operation                     | 112 |

| Figure 39 - Interrupt Timing in Prototype UVM                     | 114 |

| Figure 40 - Keyboard/VGA UVM Running on the Hypervisor            | 116 |

| Figure 41 - kmsg_hypv_send code                                   | 118 |

| Figure 42 - Crossing the Semantic Gap                             | 119 |

| Figure 43 - UVM Message Receive Interrupt Handler                 | 120 |

| Figure 44 - Launch Second UVM Code                                | 122 |

| Figure 45 - Complete UVM Architecture                             | 123 |

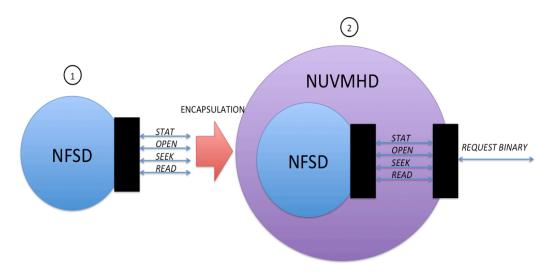

| Figure 46 Encapsulation of NFSD into NUVMHD               | 130 |

|-----------------------------------------------------------|-----|

| Figure 47 - NUVMHD Send and Reply Structure               | 130 |

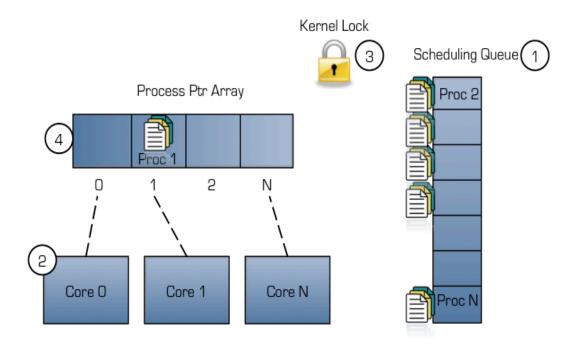

| Figure 48 - Scheduling Software Components                | 138 |

| Figure 49 - Code to Schedule Next Process                 | 143 |

| Figure 50 - Dynamic Load-Balancing Code                   | 144 |

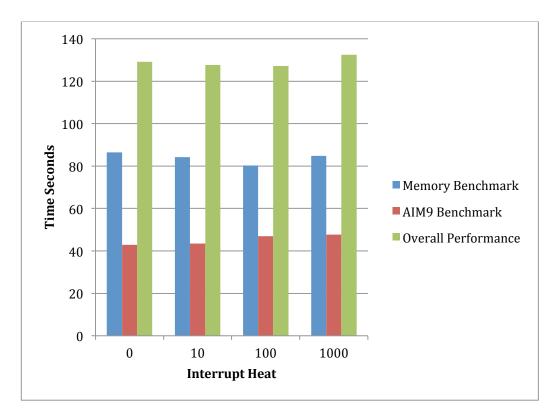

| Figure 51 - Diffusion Performance as Interrupt Heat Rises | 149 |

## **List of Acronyms**

Address Resolution Protocol **ARP** Address Space Layout Randomization **ASLR** Advanced Configuration and Power Interface **ACPI APIC** Advanced Programmable Interrupt Controller **Application Processor** AP API **Application Programming Interface BIOS** Basic Input/Output System **Basic Virtualization** VT-x **BSP Bootstrap Processor** Control Register CR **CHS** Cylinders, Heads, and Sectors **Destination Format Register DFR** Direct Kernel Structure Manipulation **DKSM DHCP** Dynamic Host Configuration Protocol Extended Feature Enable Register **EFER Extended Page Tables EPT GNU** Assembly **GAS** Implementation of the Preboot eXecution Environment **iPXE** Input Output Memory Management Unit Virtualization VT-d Input/Output Advanced Programmable Interrupt Controller I/O APIC **Inter-Processor Interrupts IPI**

**ICRH**

Interrupt Control Register High

Interrupt Control Register Low **ICRL** Interrupt Virtualization APIC-v Lightweight IP **LWIP** Logical Destination Format Register LDR **MBR** Master Boot Record Memory Management Unit **MMU** Memory Mapped Input/Output **MMIO** Model Specific Register **MSR** Multi-Processor MP Multiple APIC Descriptor Table **MADT** Network File Sharing Daemon **NFSD** Network File System **NFS** Network Utility Virtual Machine Helper Daemon **NUVMHD** Network Virtualization VT-c No-Execute NX **PAE** Page Address Extension Page Directory Table **PDT** Page Map Level 4 Table PML4T Page Table PT Page-Directory-Pointer Table **PDPT** Port Input/Output PIO PIT Programmable Interrupt Timer Programmable Interrupt Controller **PIC**

Return Oriented Programming ROP Remote System Descriptor Pointer **RSDP** Remote System Descriptor Table **RSDT** SIMD Extension SSE Startup Inter-Processor Interrupt SIPI Symmetric Multiprocessing **SMP** Time Stamp Counter **TSC** Transition Lookaside Buffer TLB Trivial File Transfer Protocol **TFTP** Utility Virtual Machine **UVM** Video Graphics Array **VGA** Virtual APIC **VAPIC** Virtual Machine VM Virtual Machine Monitor **VMM** Virtual Switch vSwitch

#### **Chapter 1 – Introduction**

Problem: Adversaries tailor their attacks in the presence of a hypervisor, which alone cannot protect against zero-day vulnerabilities in the guest operating system

Hypothesis: The ability to conduct zero-day attacks can be reduced through hardware isolation and a minimized code surface with acceptable performance.

The approach advocated in this thesis to mitigating kernel-level zero-day attacks is to directly utilize hardware supported guest-virtual isolation in a radical new generation of hypervisor designs. These designs -- termed utility virtual machines (UVM) – improve security by eliminating the conventional kernel and replacing it with a collection of specialized virtual machines, which employ hardware protections to enforce isolation between system components such as device drivers and system daemons. This establishes a root of trust in hardware and prevents the compromise of one component from undermining the system as a whole.

There are four central challenges to this technique: Can existing hardware virtualization mechanisms be used to extend conventional inter-process communication and synchronization mechanisms (such as rendezvous and message passing primitives) to the hypervisor layer? Can virtualization support

the fragmentation of an operating system into individual utility virtual machines to support the appearance of a cohesive system? Can the resulting security features be implemented in a manner that has a minor impact to performance? Finally, can methods be devised to schedule a multiplicity of tasks across multiple cores?

#### 1. 1 Background & Motivation

Virtualization is enabled through the addition of a new layer to the software stack known as the hypervisor [1] or Virtual Machine Monitor (VMM) [2]. The hypervisor encapsulates the hardware, allowing it to be used by multiple operating system instances concurrently. This flexibility, coupled with the cost and performance advantages of sharing the underlying hardware, has revolutionized the computing industry: large numbers (i.e. hundreds of thousands) of generic hardware platforms, using multi-core blade technology, are now coupled through high-performance networking to produce a generic computing surface. Any subset of this collection can be combined to operate in tandem for a particular application using a multitude of operating systems.

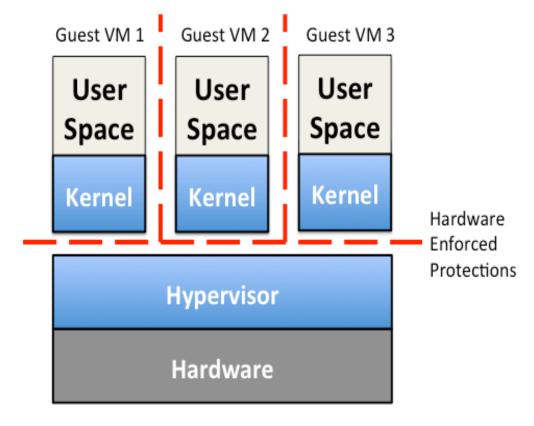

Conceptually, the hypervisor presents a virtual machine abstraction that restricts malicious code embedded in one operating system instance from affecting a different instance [3], by containing it within one virtual machine using hardware protection techniques This is achieved through type-1 or bare-metal virtualization [4] as seen in Figure 1.

Figure 1 - Bare-Metal Hypervisor

In this configuration the hypervisor controls all of the hardware on the system. On top of the hypervisor sits one or more guest virtual machines, which contains an operating system's kernel and its associated user space. The kernel provides networking, scheduling, and many other key processes. The guest's view of hardware is however tightly controlled through the Intel Virtualization suite of VT-x (basic virtualization), VT-d (input output memory management unit virtualization), VT-c (network virtualization), and APICv (Interrupt Virtualization) [5]. This provides the isolation necessary to protect other guests

from a potentially compromised guest, but does not protect data resident inside of that guest.

Unfortunately, hypervisors have introduced their own new security challenges: adversaries now actively attempt to detect the presence of an operating hypervisor in order to tailor attacks accordingly [6]. A wide range of hypervisor detection techniques have already appeared against popular systems such as VMWare, VirtualPC, Bochs, Hydra, Xen, and QEMU [7]. Often, these techniques operate by exploiting timing differences between virtualized and non-virtualized operations [8]. Alternatively, they detect unusual memory locations associated with key operating system data structures [9]. For example, the Red Pill technique works by using the SIDT X-86 instruction to determine the location in memory of the interrupt descriptor table; a machine running above a hypervisor will return a location much higher in memory than one that is not [10]. Following hypervisor detection, the adversary then attacks either the operating system, the virtual switch (vSwitch) sharing network connectivity between virtual machines, or the hypervisor itself [11].

The presence of a hypervisor has no impact on the known and unknown zero-day vulnerabilities associated with a particular operating system. As a result, any exploit that leverages a known vulnerability will operate successfully [12] against any virtual machine running the system. Packaging this exploit within a propagating virus provides the adversary an opportunity to compromise every

virtual machine in the cloud running the same instance. It is this *vulnerability amplification* that poses the most significant threat to the future of cloud computing.

After the attacker has gained a foothold and determined they are operating in a virtualized environment, they will attempt to compromise the hypervisor. This often entails chaining together multiple small pieces of kernel code known as gadgets in a Return Oriented Programming (ROP) attack [13,14,15]. This allows the hypervisor to be attacked by the code that was meant to protect it. ROP methods are made easier as *attack surface* increases, which equally raises the number of gadgets present.

ROP attacks can be built to create direct attacks against a vSwitch may undermine the operation of multiple virtual machines on a single host by denying connectivity to all of them simultaneously. The vSwitch provides the same functionality as a physical switch and in consequence exhibits the same vulnerabilities, enabling the same exploits [16]. For example, Address Resolution Protocol (ARP) spoofing, involves the interception of valid network packets by sending fake ARP packets to a switch [17].

Going after the hypervisor itself involves the direct exploitation of vulnerabilities in the hypervisor. All virtual machines executing on a hypervisor have distinct data structures, separated in hardware. This separation forms a semantic gap [18]

that prevents virtual machines from having visibility or impact upon each other's data structures [19]. Direct Kernel Structure Manipulation (DKSM) bridges the semantic gap by patching virtual machine data structures and redirecting hypervisor accesses to shadow copies. This allows the virtual machine to present false information to the hypervisor regarding the virtual machine state, which allows implants, such as rootkits [20], to persist without detection.

Virtualization provides inherent redundancy and robust, large-scale, cost-effective availability of shared resources [21]. However, this perception is tempered by the risk of vulnerability amplification and the paucity of knowledge regarding zero-day exploitation: history has shown that lack of detection does not imply lack of infection.

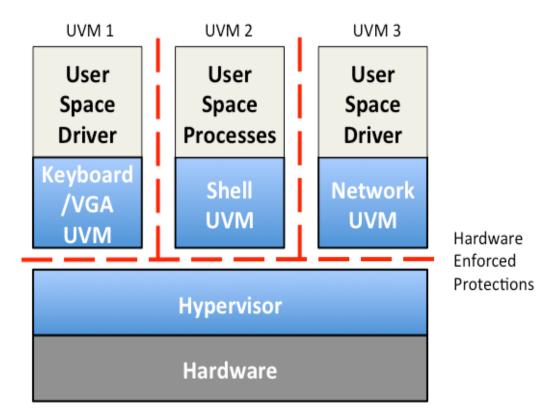

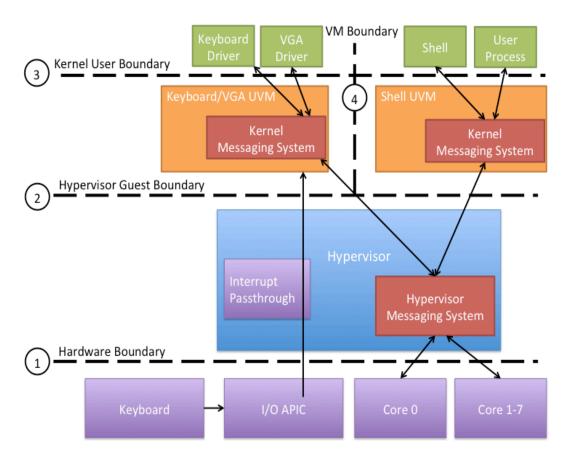

To combat these risks, termed *utility virtual machines* separate and isolate the normal responsibilities associated with a congenital kernel as shown in Figure 2.

Figure 2 - Bare-Metal Hypervisor with Utility Virtual Machines

Each UVM encapsulates a particular functionality and can include, but is not limited to, user applications, networking and Keyboard/VGA drivers. The benefit of this reorganization is that the standard kernel is eliminated as an entity and hardware isolation is enforced between each component of the system. If any particular UVM is compromised, the attacker has access to only a small subset of the system data taken as a whole. Furthermore, since most data structures and code are unique to the infected UVM, the attacker has little information to glean on other running UVMs. This is in stark contrast to the standard model, where a compromise of the network would give an attacker complete control of the guest

and all of its associated data, including many other operating system specific tasks and data structures.

This new approach has only become possible in the last ten years: Moore's law [22] has provided a rapid growth in the areas of multicore [23] and virtualization [24] technologies. The coupling of these two mechanisms at scale forms the basis for the UVM architecture. Each UVM is assigned a dedicated number of cores for optimal performance of its assigned individual task. Virtualization allows for the operation of non-homogenous VMs making it more difficult for an adversary to cross the semantic gap. Furthermore, the fragmentation afforded by UVMs has the dual benefit of increasing attacker workload and decreasing the attack surface, benefits that will be discussed in detail in chapters 4 & 5.

#### 1.2 Approach

A complete operating system based on the UVM concept has been realized in the latest generation of a research operating system called *Bear* [25] under development at Dartmouth College. This system shares its core motivations of security, modularity, and resilience with MINIX [26], but directly integrates a Symmetric Multiprocessing (SMP) micro-kernel with an associated SMP hypervisor, using Intel x86-64 architectural support including VT-x and VT-d extensions. In previous versions of the Bear system, these technologies were coupled with extensive code sharing between the micro-kernel and hypervisor,

which served to reduce the attack surface and space of potential vulnerabilities [27].

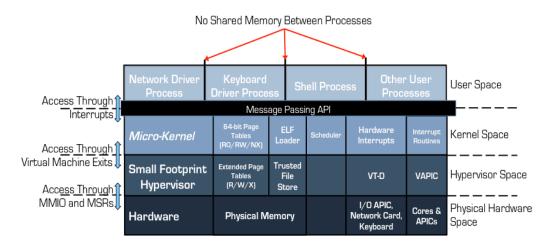

Figure 3 shows an overview of the original system that serves to illustrate the interplay of security concepts employed in the design. Like the MINIX microkernel, device-drivers are operated from user-space where they can be refreshed in a manner similar to the MINIX regeneration process [26]. However, Bear intentionally makes no attempt to detect intrusions or failures; instead, potentially compromised device drivers, when not in use, are non-deterministically refreshed to deny persistence, regardless of their infection status. A similar approach is taken to deny persistence in the micro-kernel: the hypervisor nondeterministically refreshes the micro-kernel periodically from a gold-standard, either at pre-arranged or non-deterministic times. Gold-standard images are stored within a read-only ramdisk, uploaded using iPXE's signed and encrypted bootstrapping. Each time a component of the system is refreshed it is also diversified at load time [28]. This process, an enhanced form of Address Space Layout Randomization (ASLR), ensures that no two running instances of a binary share an exploitable address -- including the hypervisor itself, the micro-kernel, device drivers, system daemons, and user processes. This denies surveillance and reverse engineering while throttling vulnerability amplification caused by using the same micro-kernel throughout a cloud or high-performance computing infrastructure.

Figure 3 - Bear System Layout

In common with other designs, the original micro-kernel handles multi-core scheduling of user processes and is responsible for protecting the micro-kernel from user processes, and user processes from each other. All processes and layers are hardened by strictly enforcing MULTICS-style read, write, and execute protections [29] using 64-bit x86 address translation hardware. The use of extended page table entries allows micro-kernel to be marked *execute-only*; recall that the normal x86 paging structures do not provide sufficient flexibility [30] to achieve this protection. Finally, although micro-kernel code is replicated in user processes, in common with many other operating system designs, an additional level of indirection allows its location within each process to be obfuscated [31].

Like MINIX, all potentially contaminated user processes, device drivers, and services are executed with user-level privileges and are strictly isolated from the micro-kernel via a message-passing interface. However, unlike MINIX, there is no system task, all system calls, IO, and process scheduling is achieved by

interrupt handlers with kernel privileges. These handlers mediate between processes and the kernel to rigidly enforce the interface. Unlike the MINIX rendezvous mechanism [32], Bear uses an asynchronous, bounded buffer interface similar to MPI [33] that provides a single uniform treatment of system calls, interprocess, and off-chip inter-processor communication on blade servers. Similarly, in the rare event the micro-kernel is unable to complete a user process request, a VMExit may be generated, which is handled by the hypervisor in a similar fashion as to the micro-kernel handles interrupts. The hypervisor enforces the protection layer between the micro-kernel and the underlying physical hardware. The hypervisor having full control of the physical hardware accesses functionality as it is needed through memory mapped I/O (MMIO) and Model-Specific Registers (MSR).

The rich collection of modern features in the Bear system provides the transition point to the UVM security model. The most important concept is the rigid enforcement of MULTICS protections [29] through virtualization hardware. These protections ensure that device drivers exist solely in user space as a single process that does not require kernel level privileges. Using this isolation model as a jumping off point, the functionality of these singular device driver processes can be transferred from a *process* to a UVM. However, this can only be accomplished by overcoming the core key research challenges: building a hypervisor message passing system, structural reorganization around utility virtual machines, performance optimization, and scheduling.

Since message passing is central to MINIX and the Bear kernel alike, it will also become central to UVMs as they communicate requests between each other. This communication requires the creation of a message-passing interface to the hypervisor. This is particularly interesting facet of the research, since many members of the research community seek to operate within the hypervisor for the smallest possible time for efficiency. A message-passing interface requires additional compute cycles inside the hypervisor and consequently has the potential to slow the guests operation to some degree. However, since each UVM is not a full-fledged kernel, it was initially unclear how the reorganization would impact performance overall. As we will see, utility virtual machines trade what were once kernel cycles for hypervisor cycles. Unexpectedly, the performance results developed in this thesis show that the separation of duties and direct reliance on modern hardware actually generates a net *improvement* in performance (Chapters 4 & 5).

To demonstrate the concepts, the latest generation of the Bear operating system is realized through a collection of three individual UVMs: a network UVM, a keyboard/VGA UVM, and a shell UVM that handles the responsibilities of a typical shell and is capable of scheduling user processes. Isolation between UVMs is enforced through hypervisor protection hardware and only legitimate communication can occur through the hypervisor messaging system. The

hypervisor schedules these three UVMs statically on bootstrapping to a set number of cores present on the system.

A critical aspect of cloud computing and computing in general is the requirement of efficient, reliable, and scalable scheduling of processes. These aspects become more critical as multiple UVM's schedule multiple processes simultaneously. Specifically, one UVM may run a scheduling algorithm to provide fairness, while another could pin processes to specific cores with particular hardware. To meet the criteria of efficiency, reliability, and scalability a diffusive scheduler [34] was explored within the shell UVM. This algorithm had previously been shown to be simple, scalable, and have attractive convergence properties under large scale simulations, but had not been previously been employed in practical systems.

#### 1.3 Performance Metrics

Industry standard methods are used to assess performance in this thesis. The performance of the UVM system has been compared to standard monolithic operating systems with associated hypervisors and the original Bear system, operating on generic Dell workstations. Two benchmark suites were employed: To assess system memory utilization, a test suite developed by Chuck Lever and Chuck Boreham at the University of Michigan measures the performance of *malloc()* in a multithreaded system [35].

In addition, the popular AIM9 benchmark suite is used to measure processor synthetic overhead through its addition, subtraction, and multiplication modules [36]. These tests stress the system by executing instructions that specifically target the internal processor logic.

Beyond system benchmarks, recent studies have confirmed our intuition that the number of vulnerabilities in a code base is proportional to its size [27]. Consequently, attacker workload is estimated in terms of lines of source code loaded in memory. Each utility virtual machine presents a unique sand boxed attack surface, which can be enumerated. The CLOC utility was used to count these lines of code [37].

#### 1.4 Contributions

The contributions of this research are:

- A novel system architecture based on the concept of Utility Virtual Machines in which the operating system kernel is replaced by a collection of virtual machines, each encapsulating a distinct system function. This architecture improves security by sandboxing system functions within virtual machines using hardware protection techniques.

- A body of practical implementation techniques that serve to realize systems based on UVM's.

- A practical demonstration and experimental analysis of UVM architecture that assesses memory utilization, processor performance, and impact on attacker workload based on three exemplars:

- A Network UVM that comprises all the functionality to encapsulate a network card driver, network file system process, and network stack.

- A keyboard/VGA UVM that contains all I/O functionality to interact with users [38].

- A shell UVM that isolates the functionality to fork and schedule user processes on multiple cores [38].

- A generalized rendezvous-style message-passing system between UVMs

that operates through the hypervisor, is adapted from those employed to

provide system calls [38], and leverages modern APIC-interrupt

mechanisms for efficiency

- A practical heat diffusion scheduler to improve performance of process scheduling in the UVM architecture with an associated body of experimental analysis.

- A novel hypervisor shim that inserts itself under a running micro-kernel

and leverages virtualization technology to enforce execute-only memory protection [30].

- A practical method for combining iPXE, DHCP, TFTP, and NFS to load binaries across the network and diversify them at load time [28].

- Creation of a micro-kernel that is treated as a dynamically linked library,

which enables kernel diversification on a per-process basis [31].

- A body of practical techniques for realizing advanced hypervisor and micro-kernel designs that leverage modern 64-bit multicore and virtualization hardware. (Submitted to software practice and experience).

#### 1.5 Thesis Organization

In outline, the thesis is divided into the following chapters:

Ch 1: *Introduction* states the hypothesis and the associated challenges posed by the thesis, motivates the research, identifies the contributions, and describes the assessment metrics used in analysis.

Ch 2: *Related Work* provides a survey of the relevant literature and demonstrates the opportunity to advance system security through the techniques developed in this thesis.

Ch 3: *Symmetric Multiprocessing* describes the multicore hypervisor and microkernel created as part of this thesis. This chapter explores the design choices and specific details of bringing SMP to a system from boot to virtualization.

Ch 4: *Utility Virtual Machines (UVM)* describes the creation of the UVM rendezvous message passing system and its use to couple together the first UVM prototypes through the hypervisor.

Ch 5: A Further Abstraction: The Network UVM discusses the challenges and solutions for moving a non-trivial operating system component into a UVM encapsulation.

Ch 6: *Heat Diffusion Scheduling* details the implementation of a novel scheduling technique to improve performance in multicore environments.

Ch 7: Future Work and Conclusions makes concluding remarks on the work presented in earlier chapters and describes directions for future work.

## **Chapter 2 – Related Work**

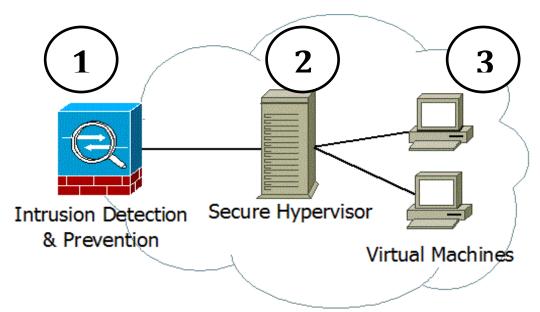

Prior to the start of the UVM work, a survey and analysis of the current security measures implemented with hypervisors to prevent ROP and other attacks was conducted. The viability of an efficient virtualization layer has led to an explosive growth in the cloud computing industry, exemplified by Amazon's Elastic Cloud, Apple's iCloud, and Google's Cloud Platform. However, the growth of any sector in computing often leads to increased security risks. This chapter explores these risks and the evolution of mitigation techniques in open source cloud computing. Unlike uniprocessor security, the use of a large number of nearly identical processors acts as a *vulnerability amplifier*: a single vulnerability being replicated thousands of times throughout the computing infrastructure. Currently, the community is employing a diverse set of techniques in response to the perceived risk. These include *malware prevention and detection, secure virtual machine managers*, and *cloud resilience*. These three categories and their roles in preventing an attacker from gaining access to the cloud are illustrated in Figure 4.

Figure 4 - Example Security Techniques in the Cloud

Omitted from Figure 4 are cloud services that provide authentication such as lightweight active directory protocol servers and trusted computing techniques as they are outside the scope of this survey. Initially, the attacker has to overcome or bypass the intrusion detection and prevention systems typically employed at the cloud boundary. They are then faced with a secure hypervisor usually installed on a single host; whose purpose is to restrict access to kernel and hypervisor data structures. Finally, cloud resilience, is used by a host to restore a single compromised or failed virtual machine to a known good state. Although not currently prevalent throughout the industry, hypervisors offer the opportunity to restrict the attacker's access to the base of the software stack. Since typically the number of vulnerabilities is directly related to the number of source lines of code [27], this would allow tight control of the hardware and allow operating system designers to build successive layers on a secure base of trust. The small size of the

hypervisor also opens the door to formal reasoning concerning its security properties [39]. Unfortunately, these ideas have yet to be cohesively integrated and their impact upon security quantified. In the sections that follow we explore the building blocks that are available for improving cloud security and assess them on the basis of their *performance impact*, ability to *reduce the attack surface*, *detect known and zero-day threats*, *resolve detected threats*, and *increase attacker workload* by denying either surveillance or persistence.

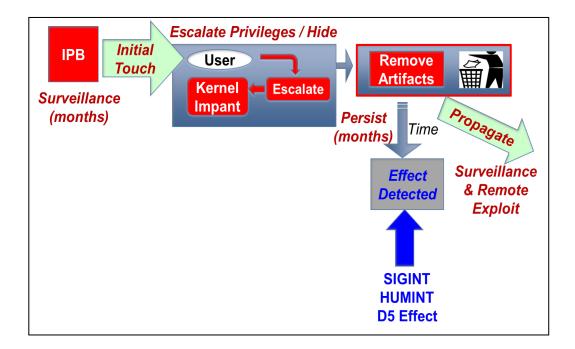

#### 2.1 Threat Model

The security implementations analyzed in this chapter and the thesis as a whole, address the threat model for intrusions employing remote control outlined in Figure 5. Attacks involve several steps that begin with *surveillance* to determine which vulnerabilities exist [40]. Vulnerabilities may revolve around specific people, processes, organizations, and network infrastructures. Based on the available vulnerabilities, the coordinated attack involves multiple initial *touches* on target networks that develop points-of-presence through some form of *implant* [41]. The initial touches may use remote user- or kernel-level exploits [42], insiders with legitimate user-level accesses [43], theft of legitimate credentials [44], supply chain interdiction [45], physical attacks at an end-point device [46], and a wide variety compromises based on radio frequency and infrastructure weaknesses. Development from the initial points of presence may involve privilege escalation [42], removing exploit artifacts, and hiding behavior [20]. On-going surveillance may involve obtaining a copy of the binary codes and

using reverse engineering [47,48] or fuzzing [49] to open additional attack vectors. The implants then *persist* for a time sufficient enough to carry out some malicious effect, obtain useful information, or propagate intrusion to other systems [50].

Figure 5 - Threat Model

Unlike the time to execute an exploit, the time spent in surveillance and persistence may range from minutes to months or even years depending upon the desired effects. Moreover, the presence of an intrusion may never be detected by network or on-host defenses but instead may be recognized only indirectly in a deviation from expected behavior, or may be derived from outside sources.

Nevertheless, each cloud security technique represents an integral building block in the multilayered defense of the cloud. Malware detection and prevention systems are the initial line of defense in preventing an attacker from gaining a foothold on a cloud. The secure hypervisors present a hardened code base that restricts access to hardware to all, but the most privileged operations. Lastly, cloud resilient solutions are present to protect against the unknown exploits, which may allow an attacker to operate on a cloud indefinitely.

### 2.2 Malware Detection and Prevention

Malware detection was one of the first techniques implemented after the introduction of hypervisors. To achieve this, researchers paired the proven technology of Intrusion Detection Systems (IDS) with the ability to hide in a virtual machine. In this scenario, the IDS still performs the same function of identifying patterns of malicious behavior on a system that may be compromised [51]; for example a proof of concept based on the Snort IDS successfully prevented a Distributed Denial of Service (DDoS) attack [52]. This implementation installed a virtual machine that ran Snort on top of the VMware hypervisor to monitor network traffic to all guest virtual machines attached to a virtual switch. Once running, the IDS dealt with DDoS attacks in two steps: Initially, attacking computers were blocked by Snort; subsequently, the virtual server automatically moved the application under attack to a new location in the cloud. This demonstrated that an IDS can function inside the cloud; however, the implementation was just as vulnerable to zero-day attacks as non-virtualized IDS's [53]: attacks were missed due to IDS configuration and the failure of signatures to detect new attacks.

The Hybrid Virtual IDS is a solution that leverages the strengths of the cloud and improves upon the previous Snort implementation [54]. The approach combines resilience of a virtual IDS and the versatility offered by a host based IDS. This is possible through the use of integrity checking [55] and system call trace analysis [56]. Integrity checking is a static detection process in which a changed file is compared to a gold standard to determine if the change is malicious. System call trace analysis dynamically flags anomalous system call behavior as potentially dangerous. These two approaches are implemented inside of a virtual machine to provide an isolated environment. A custom hypervisor is then used to ensure the isolation between all virtual machines. To provide functionality to the IDS, the hypervisor has hooks that allow the inspection of other guest virtual machines running on the hypervisor. This allows the hybrid virtual IDS to remain isolated from other running virtual machines, while still allowing it to access data from the virtual machines it is monitoring. This technique performed well in testing conducted by the authors of the Hybrid Virtual IDS, but returned unexpected performance results: as the IDS decreases the length of time between inspecting of the monitored virtual machine, the workload processing time did not increase linearly as to be expected and instead became erratic. The cause of this erratic performance is open to additional research.

With the introduction of a hypervisor and a virtualized IDS, it was only a matter of time before firewalls were moved into the cloud. One of these virtual firewall implementations is VMwall [57], which runs in the privileged virtual machine that controls the Xen hypervisor and uses virtual machine introspection [58]. This is the process of inspecting the data structures of a separate virtual machine. To enable this functionality, the Xen hypervisor has added hooks that capture all network connections created by a process. The data pertaining to these connections is then passed to VMwall for analysis. The connection is either allowed or blocked by using a whitelist (a list of approved processes and connection types). To deter false data during introspection, kernel integrity checking [59] is used to verify the state of kernel data structures in the guest virtual machines. This is necessary, as the primary method of inspecting traffic is through these data structures; malicious modification may compromise the monitoring of traffic. However, VMwall may be vulnerable to hijacking of a whitelisted process or an already established connection. The only method of detection against the compromise of an approved process is through the checksumming of the in-memory image of that process. This is performed by ensuring that the hash of a process has not changed from that of one contained in the whitelist. Due to the performance impact of hash analysis, this method is generally not implemented. Hijacking an established connection can be partially prevented through time outs associated with kernel rules contained in the whitelist. To fully prevent this type of compromise, deep packet inspection could be used, but is not currently employed by VMwall. Importantly, the employed introspection techniques cause a minimal performance impact: the additional overhead is 7% for file transfers from hypervisor to guest and 1% for file transfers

from a guest to the hypervisor. Added overhead for Transmission Control Protocol (TCP) and User Data Protocol (UDP) connections are negligible; increases are measured in microseconds.

An alternative approach to detection techniques, like VMwall and hybrid IDS, are prevention methods. One security appliance that performs prevention is Malaware, which is designed to prevent malware that tailors attacks upon detection of a hypervisor [60]. To deter this initial identification of a virtual environment, a signature based method is used. In this instance, a signature is an instruction that should not be executed by an unprivileged process. As an example, when a process such as Red Pill attempts to run the SIDT instruction, it will be flagged as malicious. However, as the authors of Malaware have stated, a signature based approach is only effective against known types of malware. To combat zero-day threats, two behavior based approaches that utilize dynamic analysis are proposed [61]. This could be accomplished by first learning the current process and its page table base address. With this, it is possible to check if the current instruction register belongs to the process' code pages. If this mapping does not exist, Malaware could flag the process as malicious. The second dynamic analysis method suggested is taint tracking. Changes to the system, otherwise known as taint, are created, when a process modifies any code or memory location. Accordingly, when taint is created in monitored locations, the offending process is immediately flagged as malicious. An added benefit of taint tracking is it defeats malicious code that has been transformed to look harmless, also known

as code obfuscation [62]. Once loaded into a monitored region, the obfuscated code is immediately marked as tainted and the associated process is flagged as malicious. Unfortunately, only the signature based piece of the detection has been implemented and no data relating to added overhead has been collected. However, the initial detection results were promising with a malware detection rate of 76%. Lastly, it is important to note that techniques that alter known memory states, such as address space layout randomization (ASLR) may increase the difficulty of this type of taint tracking [63].

Another prevention method, guest view casting [64], moves malware prevention from the guest virtual machine to the hypervisor. This approach reconstructs the data structures of the guest for analysis at the hypervisor level. This is achieved by translating guest virtual memory addresses to physical memory addresses, then reading the raw data from the guest's virtual hard drive. The reassembled state in the hypervisor can then be compared to the guest's state using viewing tools such as Windows Task Manager and memory dump to display all processes in memory. The presence of discrepancies between the two states may indicate the existence of malware in the guest. The authors have labeled this method of searching for discrepancies between states as *view comparison-based malware detection*. An outgrowth of this method is to use anti-virus software to scan the guest's state from inside of the hypervisor. The use of anti-virus outside of the guest shows that it identifies malware more effectively than anti-virus running inside a virtual machine. Additionally, performance of anti-virus is improved

outside of the virtual machine. The primary drawback to this approach is the assumption that the hypervisor has not been compromised. The authors agree that malicious code that targets the hypervisor [65] can compromise their approach.

Although detection and prevention are important, the last two decades have demonstrated that it is unlikely that malware can be eliminated completely [66]. Security researchers in an attempt to understand these attacks have to rely on system logs that lack integrity [67] and are often incomplete [68]. The ReVirt IDS [69], which runs on UMLinux [70]; was created in an attempt to improve upon these inadequacies. This is accomplished by creating logs for all of the relevant system level information needed to replay what transpired at an instruction by instruction level for a specific virtual machine. This allows administrators to determine all the relevant information pertaining to an attack. The overhead of performing these functions is 13-58% for kernel tasks and up to 8% for logging tasks.

# 2.3 Secure Virtual Machine Managers

Hypervisors have afforded researchers with new security capabilities. However, the hypervisor itself has come under attack as a way of gaining control of a system [71]. This has led to the introduction of Secure Hypervisors that reduce the attack surface and increase reliability by reducing the number of lines of code [27]. sHype [72], designed by IBM, increases security by taking the idea of control flow enforcement first seen in SELinux [73] and applying those controls

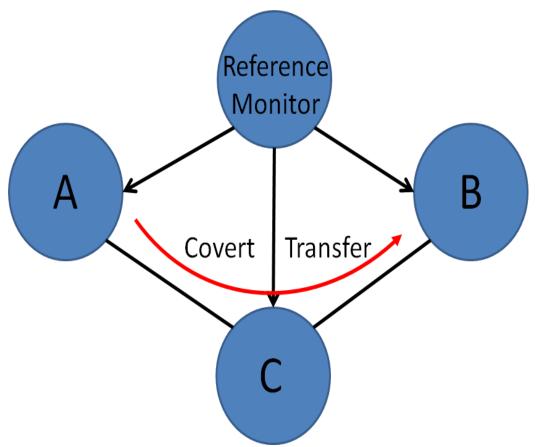

on information flows between virtual machines through a mandatory access control model. Using intricate security policies; unfortunately, these make it difficult to guarantee security and can be over 50,000 lines of code [74]. To remove this level of complexity, sHype affords the same control flow protections, but at the hypervisor level and without the need of a policy administrator. These information flows are maintained through the use of a reference monitor that decides what connections to accept and deny between virtual machines. The sHype approach creates a flexible architecture, which allows it to support many different security modules [75]. This is accomplished in around 11,000 lines of code; SELinux alone is over 85,000 lines of code.

The performance impact of sHype enforcement policies is less than 1% [72]. However, sHype's primary shortfall is that it does not completely protect against unauthorized transfer of information between two virtual machines that are not allowed to share information. Figure 6 illustrates the problem: nodes A, B, and C represent three different virtual machines and all are connected to a reference monitor.

Figure 6 – Example Covert channel

Virtual machines A and B are not allowed to share information, but both are allowed to share information with virtual machine C. A covert channel is created, when virtual machine C acts as an intermediary and passes information between A and B. In this case the reference monitor would not intervene, as it only sees information being transferred from A to C and from C to B. Fortunately, the addition of a Chinese wall (communication rules) can be added to sHype to protect against this covert channel [76]. In this case, the rule would only allow two of the three virtual machines to run at any one time. However, this method has the drawback of causing a decrease in performance of up to 9.1% [77]. This performance impact can be mitigated by performing Chinese wall policy checks

at virtual machine creation and then caching these decisions. Since, policy changes are infrequent, this configuration reduces the performance impact to less than 1% [78].

A different direction from control flow enforcement is used in the noHype hypervisor [79]. This minimalist approach removes as much as possible from the hypervisor; unfortunately, no published numbers for lines of code are available. However, the first prototype was based on a stripped down version of Xen 4.0; implying that it falls somewhere less than 1.6 million lines of code [80]. The code count was reduced by shrinking the size of the hypervisor by following four rules. First, noHype pre-allocates processor cores and memory to virtual machines. This allows the virtual machine to control its own hardware, which improves performance. Second, each virtual machine is assigned its own I/O device. Being in the cloud, it is assumed that these virtual machines only need network interface cards (NIC). The issue here is that servers have a limited number of NICs. Thankfully, newer NICs take advantage of Single-Root I/O Virtualization [81], which allows them to present themselves as multiple NICs. Thus, each virtual machine on a server is able to receive its own NIC, even if there are more virtual machines than NICs. Third, no Hype provides the user with a predefined guest virtual machine in order to control the discovery of hardware. This also prevents a user from uploading a malicious guest virtual machine, which could attack the hypervisor. Lastly, no Hype avoids indirection that occurs through the creation of virtual cores and memory, since cores and memory are assigned directly to each

virtual machine. These four principles were tested against a standard Xen 4.0 install and startup time was reduced by 1% in the noHype implementation. However, noHype loses the ability to perform any introspection of the guest virtual machines as the hypervisor is limited in functionality. Thus, a virtual machine in the noHype cloud could become infected without noHype being aware of the infection.

Another popular feature of the cloud is live migration of virtual machines [74]. This can be seamlessly accomplished with little downtime thanks to virtualization. However, migrations lose the states maintained by stateful firewalls [82] and IDS' [83]. These states can be maintained using a network security enabled hypervisor (NSE-H) designed on top of the Xen hypervisor [84]. This builds on the concepts used in secure hypervisors, but adds support for secure file transfers. The performance impact of this method is measured in downtime, which is the time a virtual machine is not available during transfer. The cost of securing these migrations is up to a 15% increase in downtime versus downtime of non-secure transfers [85]. This downtime occurs for two reasons when maintaining the security context of the virtual machines being migrated. The first is the additional time needed to securely copy a virtual machine's memory space from one host to another. The second is the NSE-H security additions, as they are using additional resources on the system.

### 2.4 Cloud Resilience

An often over-looked aspect of cloud computing is *Resilience*, defined as the ability for a system to recover and continue to provide services when a loss of hardware or software occurs [86]. One such system, Cloud Resilience for Windows (CReW) [87], expands the idea of resilience to the security domain through the use of strong security in guest virtual machines [88], and introspection [89]. Implementation is on top of the 270,000 plus lines of code that comprise the kernel-based virtual machine hypervisor [90]. This has enabled CReW to effectively prevent attacks from some rootkits and repair any damage they may have caused, but at a cost to performance as the number of virtual machines increases or security level is raised. At a strict level with three virtual machines, CReW adds ~48% increase in time needed for CPU tasks and ~279% increase in time required for I/O related tasks. For the paranoid setting, CReW adds ~116% increase in time for CPU related tasks and adds ~347% increase in time for I/O related tasks [87].

A technique that builds upon the ideas presented in CReW and supports other operating systems is that of *hypervisor-based efficient proactive recovery* [91]. This approach makes the assumption that no matter what defense is implemented on the cloud, a machine will eventually be maliciously compromised or taken offline. Thus, after particular failure conditions are met, the guest virtual machine is refreshed from a gold standard. A prototype of these concepts was developed using a modified Xen hypervisor [92]. Testing has shown there is a balance

between throughput and availability. Thus, a user of this method can choose between lower throughput and higher availability or higher throughput and lower availability when faults occur.

The Bear operating system is a minimalist implementation that builds resiliency on top of a secure hypervisor [25]. A key design choice is the strong enforcement of separating core functionality into four layers, which is typical of modern micro kernels, like the MINIX operating system [93]. Importantly, the attack surface is reduced with a shared code base (>50%) of 10,903 lines of code shared between the Bear Hypervisor and Kernel. The size is attributable to a small custom hypervisor and small custom kernel. Resiliency is derived from nondeterministically refreshing the virtual machines on the hypervisor to a gold standard after a period of time. This refresh is done by starting a second virtual machine from the known valid state and then transferring functionality to it, all while simultaneously tearing down the first virtual machine. By using this method, control is seamlessly transferred between virtual machines and without an impact to performance. Also, any known or zero-day malware present on the torn down virtual machine will not be present on the newly started virtual machine.

# 2.5 Comparative Analysis

Table 1 presents a summary comparison, of the approaches based on reduction of the attack surface, prevention of zero-day threats, and overhead. The "Reduces Attack Surface" category shows that all of the technologies other than sHype and Bear rely on a large code base.

| Cloud Security<br>Implementation                       | Reduces Attack Surface (lines of code) | Malware<br>Detection | Mitigates<br>Zero-Day<br>Threats | Added<br>Overhead (%) |

|--------------------------------------------------------|----------------------------------------|----------------------|----------------------------------|-----------------------|

| Malaware                                               | > 725K                                 | yes                  | no                               | no data               |

| Guest View<br>Casting                                  | > 1,600K                               | yes                  | no                               | Reduced up to 70%     |

| Virtual Snort                                          | > 300K                                 | yes                  | no                               | no data               |

| Hybrid IDS                                             | > 300K                                 | yes                  | no                               | ~4-36%                |

| VMwall                                                 | ~ 1,600K                               | yes                  | no                               | 1-7%                  |

| ReVirt                                                 | ~ 1,800K                               | no                   | yes                              | 8-58%                 |

| NSE-H                                                  | > 1,600K                               | no                   | no                               | 15%                   |

| Shype                                                  | ~ 11k                                  | no                   | no                               | < 1%                  |

| Shype with<br>Chinese wall in<br>Critical Path         | > 1,600K                               | no                   | no                               | 9.1%                  |

| Shype with<br>Chinese wall<br>outside Critical<br>Path | > 1,600k                               | no                   | no                               | < 1%                  |

| NoHype                                                 | < 1,600K                               | no                   | no                               | Reduced up to 1%      |

| CReW                                                   | > 270K                                 | yes                  | yes                              | ~48-347%              |

| Hypervisor-<br>Based Proactive<br>Recovery             | ~ 1,600K                               | yes                  | yes                              | ~8-12.7%              |

| Bear                                                   | ~ 11k                                  | Not<br>Applicable    | yes                              | < 1%                  |

Table 1 - Comparison Summary of Surveyed Systems

This poses a concern, as demonstrated by the authors of "Reliability Issues in Open Source Software", who have shown that errors occur at a rate of .09 defects per thousand lines of open source code. This problem is worse for closed source

systems, with .57 defects per thousand lines of code. Although the numbers will vary with code base naturally, this result that indicates Xen will have 144 defects, KVM 25, UMLinux 162, sHype and Bear each present a single defect. An interesting comparison was provided between open source software and closed source software. Due to the partial unintended release of 300,000 lines of VMware kernel code; the code could contain up to 171 defects, which is more defects then a full install of UMLinux. Obviously, sHype and Bear systems are a bare minimum install and have less functionality when compared to the other hypervisors. This has led to the sHype architecture being ported to the Xen hypervisor by the authors of "Building a MAC-Based Security Architecture for the Xen Open-Source Hypervisor", which has the net effect of increasing functionality and potential number of defects. The key takeaway is that a small code size and open source distribution are desirable to prove a system to be reliable and secure. However, closed source systems, which are outside of the purview of this article, do exist and provide similar security features. Two such commercial hypervisors not reviewed are Citrix XenClient and HyTrust.

After evaluating each system on its abilities to perform "Malware Detection" and "Prevents Zero-Days"; there were two clear outliers. Malware detection and prevention methods primarily protect against known threats, because of their use of whitelists and signatures. However, ReVirt is the outlier in this category, as it provides capabilities to remove zero-days; unlike its counterparts, it has no ability to detect malware. Secure hypervisors restrict access to the hypervisor but

generally provide no malware detection abilities or zero-day prevention. Lastly, resilient systems such as CReW and hypervisor based proactive recovery have shown promising results in both categories. The model of whitelists and signatures is replaced with restoration upon detection of anomalous system behavior. Thus, both known malware and zero-days are removed from the system when it is restored to a valid state. Resilient systems do not prevent the initial compromise from known threats, unlike malware prevention and detection systems. The outlier in this group is Bear, which makes no attempt to check for anomalous behavior. Instead, it assumes the system will eventually be compromised and therefore refreshes the system non-deterministically. This has the same end result of removing any known or zero-day attacks that may be present, but also invalidates surveillance and prevents persistence. Nevertheless, the effectiveness of resilient systems warrants further research.

The final category of "Added Overhead" is important, as no technique should overly impact system performance. Both secure hypervisors and malware prevention and detection schemes can minimally impact and in some cases improve performance. The larger resilient prototypes such as CReW and hypervisor proactive recovery have not yet reached this level of performance. Bear however, has had a negligible impact on performance when refreshing virtual machines. Research into future resilient system implementations should aim to maintain the performance levels set by intrusion detection and prevention systems, secure hypervisors, and the Bear operating system. This can be achieved

by leveraging the proven practices of either adding functionality to the hypervisor as seen in Guest View Casting or reducing the hypervisor foot print as accomplished by NoHype and Bear. Once this performance requirement is met, further capabilities can be added to resilient systems, which allow for the creation of a new cloud security architecture.

#### 2.6 Related Fields of Work

One field of study that has not been included in this survey is the idea of trust [94] in regards to the unauthorized access of data. One approach to handle trust in data security is that of security labels in the cloud [95]. The goal of this approach is to isolate customer virtual machines from each other to prevent data leakage across virtual machines. This work is an enhancement of a trusted hypervisor that extends trust to network storage [96]. In regards to privacy, customers are concerned that their personal information will be leaked to those who should not have access to it. A current solution to this problem is the use of encryption with access control [97]. Using public key cryptography in the cloud, the user can be sure that their data is safe and only they have access to it.

## 2.7 Summary

All of the techniques reviewed in this chapter have produced gains in making cloud computing more secure. Most of the solutions strive to race to the bottom of the software stack to combat known risks, rather than unknown zero-day risks. Moreover, it is currently left up to the cloud provider to pick from a grab bag of

techniques to secure their infrastructure, which often times reduce performance in a time sensitive environment. This has led to a diverse set of approaches in cloud security, each with its own goals.

However, many of these same methods have increased the size of the code base of both the kernel and hypervisor. According to Pandey et al., this represents a real risk in that additional bugs may be present in the code. These same bugs may lead to real vulnerabilities, which coupled with the large *attack surface* of the system provide the perfect environment for ROP attacks. All of this is only made worse by the homogeneity of the cloud running thousands of copies of the same virtual instance.

Thus, a different approach is needed that combines the most successful techniques to leverage multiple cores with hardware virtualization security in new ways. A new cloud infrastructure should follow the example of noHype to minimize the hypervisor *attack surface*. From there to break the monotony of guest virtualization, the standard kernel should be broken into smaller pieces that provide individual services. These smaller VMs can then be sandboxed through hardware isolation in a manner that is similar to sHype. By controlling access and information flow to these systems, anomalies due to malicious behavior can be quickly isolated and resolved. By doing all of this, a new utility virtual machine architecture would be created that increases *attacker workload* and reduces the *attack surface* used in ROP attacks.

# **Chapter 3 – Symmetric Multiprocessing**

The utility virtual machine architecture requires the linchpin of modern computing that is x86 symmetric multiprocessing. These multiple cores are required for static assignment to UVMs to provide both security and timely performance. Therefore, a solid understanding of these technologies is critical not only for this work, but also to any developer entering the field.

Unfortunately, the complexity associated with discovering, enabling, using, and virtualizing multiple cores has created a paucity in the available documentation, transferable knowledge, and readable code exemplars. This chapter describes our experience in overcoming these hurdles in the design of a from-scratch, multicore operating system – *Bear* – for utility virtual machines. In particular, intricacies involved in the development of a multi-core micro-kernel with an integrated multi-core hypervisor are traced. By exploring the implementation details, from bootstrapping through core virtualization to process scheduling, this paper aims to fill the knowledge gaps, highlight potential pitfalls, and introduce multicore development in a concise start-to-finish exemplar.

### 3.1 Introduction

Sadly, it has become increasingly difficult for systems programmers and developers to leverage the full features of x86-64 technology effectively. For example, the documents containing the information for finding, bootstrapping, and operating multiple cores are spread across multiple separate large manuals

including, the 1,056 page Advanced Configuration Power Interface (ACPI) Specification [98], the 97 page Multi-Processor (MP) Specification [99], and the 3,463 page Intel or 664 page AMD Software Developer's Manual [5,100] respectively. These specifications are in turn maintained by a multitude of parties, each with their own vested interests. For example, the MP Specification written by Intel was deprecated in favor of ACPI, which was written by a consortium of computer hardware and software manufacturers. The ACPI specification was then absorbed into the Intel written 1,084 page Extensible Firmware Interface (EFI) Specification [101]. A similar consortium of hardware and software manufacturers soon absorbed the EFI Specification into the 2,637 page Unified Extensible Firmware Interface (UEFI) Specification [102]. Fortunately, each newer specification is required to be backwards compatible with any of the older specifications to support legacy specifications. This limits the reading material for an entry level SMP programmer to the 5,280 combined pages of the MP specification, ACPI specification, Intel manual, and AMD manual. Unfortunately, Intel and AMD add to this level of complexity with their x86 chips, which support many operation modes, be it through legacy Port I/O, Memory Mapped I/O, or Model Specific Registers. These backwards compatibilities sometimes have a peculiar set of consequences.

Recently, the most significant problem for X86-64 processors, stemming from backward compatibility, resulted in a privilege escalation attack that gives an adversary full control of the system [103]. In this example, the enduring backward

compatibility concerns the ability for the processor to move internal memory mapped I/O control registers. This feature was provided so that the processor could move its own registers to a new memory location if software was already using the same memory address; a valuable capability when x86 processors are operated with 32-bit addressing and virtual memory is limited to only 4 GB. In practice, with the introduction of 64-bit addressing (x86-64), the potential for overlap rarely occurs since virtual memory was expanded to 256 TB; however, the feature to move the processors memory mapped I/O registers remained in place. This alone was not a security vulnerability, until the introduction of a new layer of processor operation and security, that operates below the kernel and hypervisor, was introduced: This layer -- the system management mode (SMM) [100] -- has control over the underlying physical hardware of the system, for example, the processor cooling fans. SMM is accessed and configured through memory mapped I/O, but access to it is heavily restricted through specialized x86-64 instructions. Unfortunately, these instructions and restrictions can be completely bypassed by an attack by using the ability of the processor to move its internal memory mapped I/O addresses to memory: moving them to overlap the memory reserved for SMM. Thus, an attacker can gain control of the system, using less privileged processor memory mapped I/O registers, to read and write directly to SMM.

This example, the volume of the combined specifications, and the complexity of hardware support for security -- available through multi-core isolation,

virtualization, and 64-bit paging and protection structures -- virtually guaranties that systems designers must operate behind a impenetrable veil of interrelated constraints. Consequently, many developers reach only a superficial level of understanding and then abandon the more sophisticated concepts, relying instead upon existing implementations associated with monolithic operating systems, such as Linux [104] or hypervisors such as Xen [1]. This is particularly true of research operating systems that utilize only the most basic processor support [26,105,106].

This paper redresses these shortcomings by providing a complete path to multicore via an all-in-one description of a minimal, virtualized multi-core system composed of a micro-kernel with an integrated hypervisor. The description uses well-known implementation techniques, to focus attention on the use of the underlying architectural support. For example: cores are statically partitioned among virtual machines, each virtual machine runs a single micro-kernel, each microkernel schedules processes round-robin across cores owned by the virtual machine and mutual exclusion of multiple cores from the scheduling queue uses a single global lock (similar to early versions of Linux). These design choices can readily be improved and optimized using well known techniques that are unrelated to the underlying hardware concepts. Although reasonably straightforward, the design performs surprisingly well when compared with Fedora, Ubuntu, and Xen; mature systems that have undergone hundreds of manyears in development and optimization. This can be directly attributed to

extensive use of Intel 64-bit hardware mechanisms employed through their recommended implementation methods.

## 3.1.1 Basic Concepts

Basic Input/Output System (BIOS) [107] – The BIOS constitutes firmware installed on a system that is the first code to run when the system is powered on. The BIOS is responsible for initializing all of the core hardware components (i.e. VGA, Network, Processor Cores, Memory, etc.) into a known good starting state, specified by the hardware vendor. The BIOS specification for multicore processors, detailed in the Intel Developer Manual [5] states: "The MP initialization protocol defines two classes of processors: the bootstrap processor (BSP) and the application processors (APs). Following a power-up or RESET of an MP system, system hardware dynamically selects one of the processors on the system bus as the BSP. The remaining processors are designated as APs." Upon completing initialization the BIOS loads the Master Boot Record (MBR) from either a physical hard drive, disk, or memory disk (RAMDISK) transferred over the network. Once loaded the BIOS turns execution over to the BSP, which starts execution at the beginning of the loaded MBR.

Master Boot Record (MBR) [108] – The MBR emerged with the PC DOS 2.0 system in 1983 and corresponds to the first 512 bytes of code loaded from disk by the BIOS; it is subsequently executed by the BSP. The MBR is restricted to 512 bytes in size, an historical artifact associated with dividing hard drives into