## Attack Mitigation through Memory Encryption

## A Thesis

Submitted to the Faculty

in partial fulfillment of the requirements for the

degree of

Doctor of Philosophy

in

**Engineering Sciences**

By

Michael J. Henson

Thayer School of Engineering Dartmouth College Hanover, New Hampshire

September 2014

| Chairman |                       |

|----------|-----------------------|

|          | Stephen Taylor, Ph.D. |

|          |                       |

| Member   |                       |

|          | George Cybenko, Ph.D. |

|          | -                     |

| Member   |                       |

|          | Eric Hansen, Ph.D.    |

|          |                       |

| Mombor   |                       |

Jeff Boleng, Ph.D.

**Examining Committee:**

F. Jon Kull Dean of Graduate Studies

#### **Abstract**

Historically, full memory encryption (FME) has been propounded as a mechanism to mitigate vulnerabilities associated with code and data stored in the clear (unencrypted) in random access memory. Unfortunately, until recently the CPU-memory bottleneck has represented a roadblock to using this concept to design usable operating systems with acceptable overheads. Recently however, a variety of commodity processors, including the Intel i7, AMD bulldozer, and multiple ARM variants, have emerged that include security hardware -- in particular, encryption engines -- tightly integrated on-chip. This innovation opens the door to a new generation of operating systems that protect data by encrypting code and data in RAM. This thesis explores this idea and introduces a collection of novel operating system technologies that provide automated, transparent confidentiality and integrity protection via memory encryption. These techniques raise the difficulty for attackers, making it significantly more challenging to determine the vulnerabilities present on a system, apply the same attack vector against multiple hosts, steal sensitive information, reverse engineer code, modify data at rest or in flight, and inject code onto a platform.

### **Acknowledgements or Preface**

I would like to thank my advisor Dr. Stephen Taylor, as well as fellow group members Colin, Jason, Kathleen, Morgon, Rob, and Steve. I also want to thank my wife Latasha and children who put up with many late nights and who inspired me to continue striving even when my time was extremely limited. Special thanks to Brianna and Elanna for covering many flights of stairs while providing me with the necessary sustenance to keep me working. Finally, I would be remiss if I did not thank my mother and father, who imparted both a strong work ethic and a love of learning.

This research is supported by the Defense Advanced Research Projects Agency as part of the CRASH program under contract FA8750-11-2-0257. The U.S. Government is authorized to reproduce and distribute reprints for Governmental purposes notwithstanding any copyright notation thereon. The views and conclusions contained herein are those of the authors and should not be interpreted as necessarily representing the official policies or endorsements, either expressed or implied, of the Defense Advanced Research Projects Agency (DARPA) or the U.S. Government.

"It is not the critic who counts; not the man who points out how the strong man stumbles, or where the doer of deeds could have done them better. The credit belongs to the man who is actually in the arena, whose face is marred by dust and sweat and blood; who strives valiantly; who errs, who comes short again and again, because there is no effort without error and shortcoming; but who does actually strive to do the deeds; who knows

great enthusiasms, the great devotions; who spends himself in a worthy cause; who at the best knows in the end the triumph of high achievement, and who at the worst, if he fails, at least fails while daring greatly, so that his place shall never be with those cold and timid souls who neither know victory nor defeat."

-Theodore Roosevelt

# **Table of Contents**

| Abstract                                 | i   |

|------------------------------------------|-----|

| Preface                                  | ii  |

| Table of Contents                        | V   |

| List of Tables                           | vi  |

| List of Figures                          | vii |

| 1. Overview                              | 1   |

| 1.1 Problem                              | 1   |

| 1.2 Hypothesis                           | 1   |

| 1.3 Approach                             | 2   |

| 1.4 Contributions                        |     |

| 1.5 Scope and Assumptions                | 5   |

| 1.6 Outline of the Thesis                | 7   |

| 2. Comparative Analysis of ME Literature | 9   |

| 2.1 Overview                             | 10  |

| 2.2 Monolithic Processor Enhancements    | 18  |

| 2.3 Multiprocessor Enhancements          | 25  |

| 2.4 Bus Inserts                          | 29  |

| 2.5 Operating System Enhancements        | 31  |

| 2.6 Specialized Industrial Devices       | 32  |

| 2.7 Commoditized Security Hardware       | 36  |

| 2 & Analycic                             | 37  |

| 2.9 Conclusion                                                   | 50  |

|------------------------------------------------------------------|-----|

| 3. Core Ideas and Related Work                                   | 53  |

| 3.1 Threat Model                                                 | 53  |

| 3.2 Core Ideas                                                   | 56  |

| 3.3 Related Research                                             | 60  |

| 3.4 Summary                                                      | 65  |

| 4. Static Encrypted Processes (SEP)                              | 66  |

| 4.1 Bootstrapping                                                | 71  |

| 4.2 System Initialization                                        | 73  |

| 4.3 Implementation                                               | 74  |

| 4.4 Measurement and Analysis                                     | 80  |

| 4.5 Summary                                                      | 83  |

| 5. Dynamic Encrypted Processes (DEP)                             | 84  |

| 5.1 Basic DEP Design and Implementation                          | 87  |

| 5.2 DEP Cache and MMU Enabled Implementation                     | 94  |

| 5.3 Measurement and Analysis                                     | 102 |

| 5.4 Summary                                                      | 115 |

| 6. Mutually Distrusting Processes (MDP) and Exploring Protection | 119 |

| 6.1 MDP Implementation and Measurement                           | 119 |

| 6.2 Exploring Protection                                         | 123 |

| 6.3 Summary                                                      | 130 |

| 7. Future Work and Conclusions                                   | 132 |

| 7.1 Future Work                                         | 132 |

|---------------------------------------------------------|-----|

| 7.2 Conclusions                                         | 136 |

| References                                              | 140 |

| Appendix 1: Python Code for Board Memory Initialization | 160 |

| Appendix 2: IMX53 Modified Linker Script                | 167 |

# **List of Tables**

| Table 1: Comparative Analysis of ME Techniques              | 42  |

|-------------------------------------------------------------|-----|

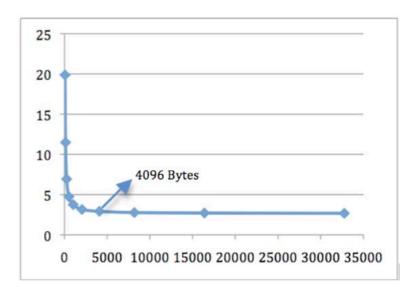

| Table 2: Overhead for Decryption of Various Sizes of Memory | 81  |

| Table 3: Context Switching Microbenchmark                   | 106 |

| Table 4: Page Allocation Microbenchmark                     | 109 |

| Table 5: Overhead for 128 KB Heap Object FFT                | 113 |

| Table 6: Overhead for 16 KB Heap Object FFT                 | 114 |

| Table 7: MDP Measurements                                   | 122 |

| Table 8: ISR Code Injection Test Results                    | 130 |

# **List of Figures**

| Figure 1: Vulnerable Memory Hierarchy                                 |

|-----------------------------------------------------------------------|

| Figure 2: Redundancies in 128-Bit Sections of Binary                  |

| Figure 3: Pseudo One-Time Pad Encryption                              |

| Figure 4: SMP Architecture with Memory Encryption Support             |

| Figure 5: SecBus Hardware Augmentation Model                          |

| Figure 6: Threat Model                                                |

| Figure 7: Processor Boundary and Emerging Security Hardware           |

| Figure 8: IBM PCI-X Cryptographic Coprocessor                         |

| Figure 9: IMX53 Development Board                                     |

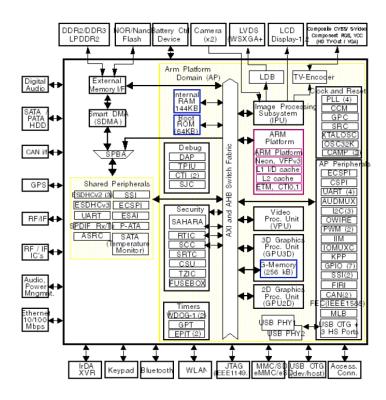

| Figure 10: IMX53 Simplified Block Diagram                             |

| Figure 11: Static Encrypted Processes Overview                        |

| Figure 12: Graph of Cycles per Bit Cost of Decryption                 |

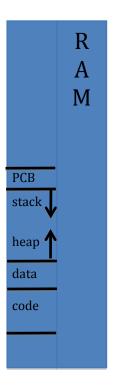

| Figure 13: Process Segments in Bear ARM                               |

| Figure 14: Dynamic Encrypted Processes Overview90                     |

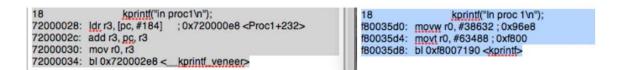

| Figure 15: Kprintf() Veneer and Normal Kprintf92                      |

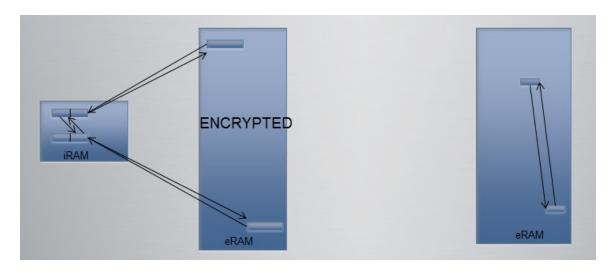

| Figure 16: Code Before and After Movement to iRAM94                   |

| Figure 17: Process Control Block (PCB) Before and After Encryption98  |

| Figure 18: Process Output with Hard Coded PID                         |

| Figure 19: Process Output with Hard Coded PID-Instr Cache Disabled101 |

| Figure 20: Protected and Unprotected FFT                              |

| Figure 21: Exception Output from Code Injection     | 128 |

|-----------------------------------------------------|-----|

| Figure 22: Process Code Before and After Encryption | 129 |

## **Chapter 1: Overview**

#### 1.1 Problem:

How can attacks against plaintext code and data residing in large random access memories be mitigated?

#### 1.2 Hypothesis:

The vulnerability associated with plaintext in memory can be eliminated, with reasonable performance impact, by *memory encryption* on security-enhanced processors.

#### 1.3 Background Synopsis

Trust as defined in computing systems is concerned with providing guarantees on functionality and security associated with a system design. Typically trust emanates from a careful combination of core hardware and software components that in tandem form a trusted computing base (TCB). This base is often used either to protect the critical core associated with a sensitive or proprietary software or it can be amplified to protect larger portions of a system.

In operating systems, a trusted base can be used to protect core kernel functions. Several examples of this include system bootstrapping via a trusted computing module (TPM) [Kauer 2007], data-at-rest protection through full-disk encryption [Casey et al. 2011], data-in-transit protection through link-level encryption [Karlof et al. 2004], and kernel operation using access control and protection schemes [Karger and Schell 1974]. Although all these technologies are valuable, they are not sufficient in-and-of themselves. They only guarantee that the system began in a trusted state and that data was confidential before it was decrypted. Unfortunately, systems become vulnerable whenever code and data are stored in the clear (unencrypted) within random access memory. This creates numerous vulnerabilities at every level of the software stack. These vulnerabilities have consistently been exploited to gather confidential information (such as encryption keys) and inject malicious code in order to overcome access controls and other protections.

#### 1.4. Approach

Recently, a new generation of commodity processors have appeared that include security technologies, such as encryption engines, on-chip within the trusted boundary provided by the processor. These processors include the Intel i7, AMD bulldozer, and multiple ARM variants. The creation/use of such processors begs the question: Can these technologies be leveraged with sufficiently low overhead in order to improve operating system security? This thesis explores the idea of enhancing security through *memory encryption*. In particular, it introduces three new technologies:

• Static Encrypted Processes: This technology employs one-time decryption within

the trusted boundary. Since the one-time cost of encryption is amortized over the life of a programs execution, its overhead is negligible. The technique can be used to protect industrial control systems employing microcontrollers and other real-time processors. These devices typically lack memory management and make little to no use of cache.

- Dynamic Encrypted Processes: This technology provides a general, full memory encryption mechanism for code and data. It is appropriate to any multi-tasking operating system that employs a memory management unit (MMU) and cache including smart phone and other mobile computing devices. Two microbenchmark programs targeting the specific areas where overhead is introduced (context switching and cryptopaging of heap and code) show reasonable performance impact of approximately .12% and 1.2% per minute respectively given a page size of 4 KB and typical mobile smartphone workloads.

- Mutually Distrusting Processes: This technology extends dynamic encrypted processes to protect processes from each other by uniquely keying each process.

At its finest granular level, this technique induces a performance penalty of approximately 1920 cycles or 2.4 microseconds per context switch (or about 480 microseconds per minute) for the key search—an extremely small overhead for the additional protections afforded.

Collectively, these technologies *increase attacker workload* by ensuring that both code and data are always encrypted outside the trust boundary afforded by the processor. To overcome this barrier requires physical access and exotic reverse engineering techniques, such as acid etching, that are generally the domain of only a few, highly

skilled, internationally recognized, specialists in reverse engineering. A side-effect of the approach is that it introduces a *synthetic diversity* into code and data: every processor's image is completely different in RAM. This makes it significantly more difficult to determine the vulnerabilities present on a particular system, use the same attack vector against multiple hosts, or steal sensitive code and data, perform reverse engineering of code, modify data, and inject code.

#### 1.4 Contributions

The core contributions of this thesis are:

- The first practical full-memory encryption system implemented on a generalpurpose commodity processor.

- A survey and comparative analysis of memory encryption techniques covering three decades of research with proposed solutions; these employ widely varying assumptions and experimental conditions [Henson and Taylor 2014].

- A collection of novel memory encryption techniques providing synthetic diversity

and increasing attacker workload. These techniques protect against software and

hardware based confidentiality and integrity attacks; the techniques are portable to

currently deployed general-purpose, security-enhanced processors [Henson and

Taylor 2013A and B].

- Analytical results that include performance benchmarks and analysis on the overhead of memory encryption down to *process segment granularity* [Henson and Taylor 2013B].

- Empirical evidence and analytical analysis that demonstrate protection through memory encryption against confidentiality and integrity attacks.

Techniques to employ self-modifying code within the memory hierarchy to achieve memory encryption.

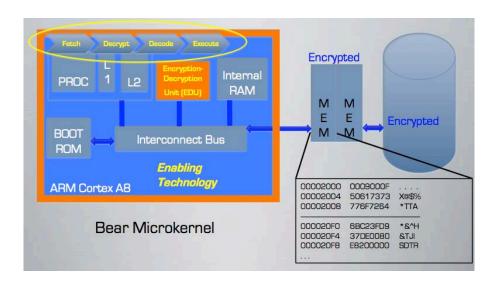

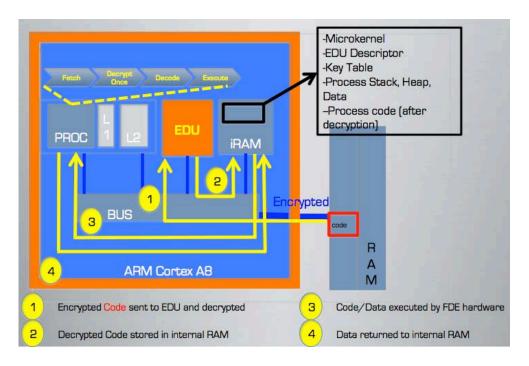

These techniques and technologies have been demonstrated in proof-of-concept implementations and exemplars. Memory encryption has been implemented on the ARM Cortex A8 processor to provide *automatic* and *transparent* protection for applications. This is achieved through extensions to a secure microkernel – Bear – under development within our research group at Dartmouth. These extensions involve modifications to linker scripts, initialization, process creation and context switching routines as well as new modules for interfacing with the A8's on-chip encryption decryption unit (EDU). The ideas have been demonstrated by encrypting processes while they reside in external RAM (eRAM) thereby adding synthetic diversity. The concepts cover application deployment regimes that range from unsophisticated microcontrollers, with no memory management unit (MMU) and cache, to full-functioned multi-processing operating systems utilizing a memory management unit (MMU) and L1/L2 cache. Various granularities of protection are considered from a complete code base to individual process. Finally, exception-handling routines have been developed and experiments executed to understand the protections afforded against code and data injection.

#### 1.5 Scope and Assumptions

The work described in this thesis extends the base of technologies available for *trusted computing*. While definitions of trusted computing abound, in this thesis it is defined as the process by which a trusted subset (software and hardware) of a system, known as the *trusted computing base* (TCB) is *amplified* to provide security assurances about the operation of the larger application or system [Smith]. Hardware components of

the traditional TCB include encryption coprocessors, random number generators, and small amounts of protected space for operation on sensitive code and data. The main application of trusted computing in operating systems design is for "trusted boot" in which the TCB checks the integrity of each component in the boot process, perhaps halting the boot process when a problem is discovered [trusted boot]. Additionally, the TCB has been used as a means for providing digital rights management. While the underlying security and integrity of hardware are often assumed to be axiomatic by those programming higher layers, this is not typically the case [Arbaugh et al. 1997 Aegis]. The inclusion of security hardware within commodity processors means that these general purpose CPUs may now be treated as part of the TCB. While the processor boundary may not have been designed to meet stringent guidelines, such as the PCI, it does, however, provide natural barriers to penetration and observation [Vandana 2008]. The work in this thesis seeks to expand upon current trusted computing capabilities such as trusted boot by continuing to protect applications dynamically as they execute. While memory encryption provides significant protection against multiple attack vectors, it should be used as part of a defense-in-depth solution including other trusted computing capabilities such as trusted boot as well as encryption of data-at-rest.

Any security can be circumvented given enough resources and motivation and memory encryption is no exception. The goal of the work, to *increase attacker workload*, can be applied under two alternative scenarios: In any time-sensitive operation, as occurs on the battlefield, an increase in attacker workload serves to force the adversary outside of the useful timeframe of any sensitive data collected. For a commercial example, the increased workload would influence the attacker to choose a

weaker attack surface, on a different device (preferably at another business).

The use of any encryption technique begs the question of key generation, delivery and escrow. Additionally, protecting programs from static analysis means that they must only be stored in an encrypted form. While this work explores some core ideas that can be applied to satisfy these questions, they have not been fully implemented. This thesis concentrates on designing and quantifying memory encryption systems on a general-purpose processor; other issues, while important, are ancillary.

Finally, it is useful to point out that there are many similarities between the goals of sophisticated attackers and law enforcement with regard to the acquisition of sensitive information from the memory of a device. Therefore, throughout this thesis, the terms attacker and forensic investigator may be considered synonymous.

#### 1.6 Outline of the Thesis

The structure of the thesis is divided into seven chapters:

Chapter 2 begins with the background and motivation for memory encryption. Next, a comprehensive survey of the past three decades of memory encryption research including a ground-truth comparative analysis is presented. Closely related works are included at the end of chapter 3 such that the latter part of chapter 2 (beginning with section 2.2) may be skipped without impacting the reader's understanding of the thesis.

Chapter 3 introduces the threat model, core ideas, and fundamental protections associated with memory vulnerabilities and memory encryption. This serves to provide background and motivation for the remainder of the thesis.

Chapter 4 describes *Static Encrypted Processes*, a memory encryption technology created as a part of this research. It describes the design philosophy, the encryption decryption unit (EDU) used, bootstrapping details, and other implementation details.

Chapter 5 describes *Dynamic Encrypted Processes*, its design philosophy, and extensions to include the use of cache and the MMU. This chapter also explores the issues associated with *self-modifying code* in memory encryption systems.

Chapter 6 extends the ideas presented in Chapter 4 to protect *Mutually Distrusting*Processes (MDP) from each other via an increase to key scope granularity. Examples of MDP's include applications (apps) downloaded from online stores and the issue of covert channels is discussed and evaluated in this context. Additionally, experimental results evaluating the security properties provided by memory encryption are provided.

Chapter 7 concludes the thesis, including directions for future research and observations.

# Chapter 2: Survey and Comparative Analysis of Memory Encryption Techniques<sup>1</sup>

Chapter 2 presents a survey of memory encryption techniques spanning the past three decades, as well as a thorough comparative analysis of those techniques. While all of the information gathered in the survey helped to shape and form the direction of this thesis it is not strictly necessary for the reader's understanding, however, the beginning of this chapter (here through section 2.1) and the conclusion (section 2.9) provide necessary background.

Encryption has been an important part of secure computing for decades, first used in the Department of Defense (DoD) and national agencies and then publicly beginning with public-key encryption in 1977 [Mel et al. 2001]. As public use of computers continued to grow, so did the need to secure sensitive information. In 1991, Phil Zimmerman released the first version of Pretty Good Privacy (PGP) allowing anyone to encrypt e-mail and files. In 1995, Netscape developed the secure sockets layer (SSL) protocol combining public and private-key encryption to protect online financial transactions. Indeed, encryption of *data-in-transit* has become accepted practice especially when interacting with entities where sensitive information is common (e.g. banking, medical, etc.).

Although a more recent innovation, full disk encryption (FDE) in commodity computer systems provides confidentiality of all data stored on disk (i.e. *data-at-rest*).

HENSON, M. and TAYLOR, S. Memory Encryption: a survey of existing techniques. ACM Computing Surveys 46, 4, Article 53. (March 2014).

<sup>&</sup>lt;sup>1</sup> Significant portions of this chaptered were published in:

Recent advances to the overall speed of processors and hardware-based encryption have resulted in several commercially viable FDE implementations. Software approaches to FDE include TrueCrypt, PGPDisk, FileVault, and Bitlocker. In addition, multiple hard drive manufacturers offer self-encrypting drives (SED) in which encryption is handled entirely by the hard drive microcontroller. Several factors have resulted in increasing adoption of FDE technologies by both individual users and system developers [Brink 2009], [Muller et al. 2011]. Regulations, such as Sarbanes-Oxley and the Health Insurance Portability and Accountability Act (HIPAA), have increased the requirement for privacy. The advent of mobile computing and increased movement of information over the Internet have raised concerns regarding physical access to data. Finally, numerous data breaches have been publicized raising awareness of vulnerabilities.

#### 2.1 Vulnerabilities and Exploits -- Motivation

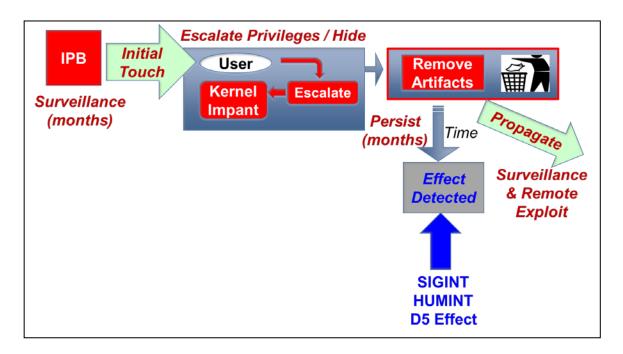

Current operating system designs have sought to utilize a *static* base of trust and extend trust into software through deliberate layering [Arbaugh et al. 1997]. Modern computer systems, even those protected by full disk encryption (FDE) [Brink 2009], exhibit a major weakness in that code and data are stored in the clear, unencrypted, within *memory and its connections*. These sensitive details are not only available to applications. They are known to persist in multiple unexpected locations (kernel and application), for longer than traditionally thought, even after an application exits [Chow et al. 2004], [Dunn et al. 2012], [Tang et al. 2012]. Unfortunately, this invalidates widely held basic security assumptions rendering it possible to gather confidential information, including encryption keys, passwords, PINs etc. that can be used to undermine trust [Halderman et al. 2008], [Boileau 2006], [Steil 2005], [Henson and Taylor, 2012]. To

exacerbate the problem, memory vulnerabilities extend to *every level of the software stack* and the opportunities for exploitation extend well beyond physical attack to include remote attacks over the Internet. Techniques have evolved that allow malicious code to be injected into device drivers, operating system kernels, and user processes.

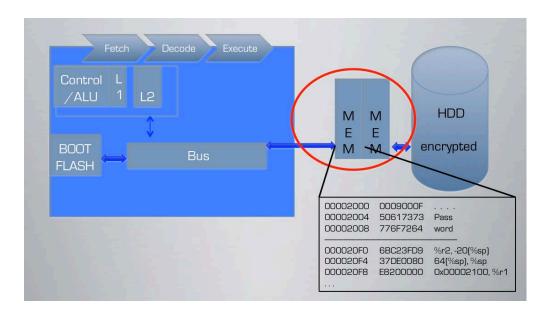

Figure 1: System with Full Disk Encryption but Vulnerable Memory and Connections

To exploit memory vulnerabilities, numerous attack vectors have been developed. In a cold boot attack, for example, memory is frozen using a refrigerant and then removed from the computer. It is then quickly placed into a specially designed system that reads out its content, targeting encryption keys and other sensitive information. This particular attack has recently been shown to be applicable to smart phone devices as well as traditional desktops via the forensic recovery of scrambled telephones (FROST) operating system [Muller et al. 2012]. Besides capturing the encryption key, FROST was used to capture other code and data to include photos, websites visited, e-mails, contact lists, networking credentials and complete ELF binaries. While this approach is novel, the

idea of recovering encryption keys from memory has been described as early as 1998 [Kaplan 2007]. Even without cooling, some information persists in RAM for several minutes [Halderman et al. 2008]. However, cooling slows down the rate of data loss, reducing recovery errors [Chhabra 2011b].

Direct memory access (DMA) attacks make use of Firewire, PCI and/or PC card protocols [Muller et al. 2011]. Direct access of memory allows an attacker to capture a copy of the entire RAM space and/or modify memory contents. The attacks have been demonstrated (with the release of "tools") in black-hat settings for bypassing Windows login screens. The routine for checking the validity of the required password is found and replaced with NOP's allowing any password to be used to gain access to the attacked system [Boileau 2006]. Unfortunately, these techniques are equally accessible to legitimate law enforcement agencies that use it for forensics investigations and criminal organizations and other attackers as well [Freiling and Vomel 2011].

One particularly effective attack, bus-snooping and injecting, allows information to be captured or inserted via the bus lines between system components [Boileau 2006]. This exploitation method has been used to undermine the Xbox gaming system. This system was specifically designed to provide a secure *chain of trust* for enforcing digital rights management (DRM). Bus-snooping was used to capture keys as they transited between read-only-memory and the CPU. These keys were then used to decrypt the secure boot loader, thus undermining the entire chain of trust. Subsequently, low-cost "mod" chips were developed that can be soldered into the gaming system bus, allowing a user to bypass DRM restrictions and play pirated games [Steil 2005]. Alternatively, the same chips can be used to run alternative operating systems on the gaming hardware

allowing it to be used for illicit purposes [Rabaiotti et al. 2010]. Far from being academic or theoretical in nature, these exploits of memory vulnerabilities have been used extensively by criminals for profit.

As encryption of data at rest becomes the status quo, attacks will begin to target vulnerable RAM. In effect, increasing adoption of these techniques has pushed the vulnerabilities associated with persistent data stored on disk down into the next level of the memory hierarchy, which itself has proven equally vulnerable. For example, *memory scraper* viruses, which target selective information from the volatile memory of point of sale (POS) applications running along side them, have been increasing since their appearance in 2008 [Baker et al. 2008]. These viruses are a subset of a larger problem with *mutually distrusting processes* (MDP). Mutually distrusting processes are those, for example, that are downloaded from an application store on a smart phone or tablet. Recent research suggests that between 0.20% and 0.47% of applications downloaded from alternative Android application stores are malicious while 0.02% downloaded from the official Android Market are malicious. While Apple goes to great lengths to review applications for security issues, malicious applications have been approved and downloaded from the official Apple application market as well [Jekyll on iOS 2013].

Fortunately, access to information in conventional dynamic RAM normally (i.e. not in the case of a cold boot attack) presents an adversary with only a *fleeting* opportunity to obtain sensitive information between power cycles. However, dynamic RAM is being augmented or replaced with new non-volatile alternatives such as flash memory, magnetic RAM, and ferro-electric RAM. These provide several benefits including energy efficiency and tolerance of power failure. Flash memory has also been

used to augment traditional RAM in the Vista and Windows 7 "ready boost" feature, whereas the other two technologies are potential RAM replacements. Unfortunately, these non-volatile memories allow information and attacks to *persist* indefinitely [Enck et al. 2008]. Interestingly, Microsoft has anticipated the security issues associated with persistent memory and has designed the ready boost feature to encrypt all contents of flash making it difficult for forensics investigators to recover useful data [Hayes et al. 2009]. If these memories are adopted in future architectures, without adequate attention to encryption or other protections, there is the potential that memory based attacks will become more prevalent.

There are three general attack vectors as described in [ARM security]: software based *hack* attacks, low-budget hardware attacks known as *shack* attacks, and resource intensive *lab* attacks. The attack vectors previously described fall into the first two of these categories. While many efforts concentrate on mitigating software-based attacks, such as buffer overflows, comparatively little effort has gone into preventing shack attacks. This may be partially explained by the difficulty in addressing attacks where an adversary has physical access of a system, for example, insiders. Shack attacks include those highlighted above such as bus-snooping and injecting, cold-boot attack and DMA attacks. Lab attacks involve significant time and equipment and examples include etching away chip walls with acid to reveal internal bus lines for microprobing, or electromagnetic and power analyses among other side channels [Ravi et al. 2004]; [Kocher et al. 1999]. For systems relying on *software based encryption*, key expansion tables (e.g. AES) are subject to cache attacks; a malicious process (MDP) tracks and

times cache accesses [Osvik et al. 2005], [Mowery et al. 2012]. The typical target of all of these attacks is the encryption key hidden within the chip boundary.

In general, encryption is used to provide four basic properties of protection: confidentiality, integrity, authentication, and non-repudiation. In trusted computing and operating system security these properties are realized through authenticated booting, ensuring that program code is not changed before it is loaded into memory, memory authentication, ensuring that program code is not changed during use, and attestation, ensuring that hardware and software have not been altered. Trusted software components, which make up part of the trusted computing base (TCB), are booted and verified producing a chain of trust, without which the security mechanisms could be compromised before the system is initialized. While few works discuss the implementation of these other mechanisms, most discussions assume that these components are functional and thus focus on the overhead of ME in the steady-state. Other important assumptions often include mechanisms for secure code delivery, key creation and escrow, inter-process communication, and I/O protection among others. Memory authentication is often closely associated with memory encryption solutions; however, a thorough survey of memory authentication mechanisms is available [Elbaz et al. 2009].

Memory encryption is solely concerned with the *confidentiality* of data and code during execution, with the express purpose of increasing attacker workload associated with crafting exploits and stealing sensitive information. It is interesting to note, however, that memory encryption also hampers attempts to inject code, which is generally assumed to require memory authentication. An adversary lacking an

encryption key would be unable to successfully change an encrypted binary, as decryption would result in corrupt code and likely program termination [Barrantes et al. 2003]. Early work associated with full memory encryption (FME) was dominated by the desire to provide digital rights management and in particular to prevent the theft of intellectual property associated with program source code. This is still the primary purpose in some systems (e.g. gaming systems), but more recently these techniques have become recognized as a method for removing vulnerabilities and protecting system users.

There are two general approaches to providing confidentiality with encryption that are commonly used in computer architectures based on symmetric or public key encryption techniques. Symmetric key encryption is based on a shared secret (key), and is generally held to be more efficient (i.e. on the order of 1,000 times faster) but it does not provide non-repudiation, and it requires a non-trivial trusted key distribution scheme [Kaplan 2007]. Three common algorithms are typically used to realize this approach based on DES, Triple-DES, and AES. Public-key encryption involves the use of two interlocking keys, one that is held privately and the other that is published, from which all four properties of protection, including non-repudiation, can be realized. This scheme has the advantage in that public keys can be distributed across open networks. A broad variety of books are available that describe these core ideas, [Mel et al. 2001] is particularly accessible. In light of the speed and complexity involved in public key encryption, it is unsurprising that the memory encryption literature typically espouses symmetric key cryptography. However, delivery of encrypted code over the network may be facilitated using the public key model [Kgil et al. 2005].

Unfortunately, computer users have consistently demonstrated an aversion to any form of increased response time, even when associated with increased security. Studies suggest that delays of longer than 150 ms are perceptible to users [Muller et al. 2011]. Full disk encryption has only become viable because overheads have been reduced to acceptable levels. Achieving similar levels of acceptable performance for memory encryption offers a far more significant challenge in that there is an existing, growing, and well-documented speed-gap between processors and memory. Improvements in processor speed are outpacing improvements in memory speed by an average of 18% per year [Hennessy et al. 2006]. Adding encryption latency to this already strained interface may require an overhaul of the basic fetch-decode-execute cycle employed by processors.

Added to the complexities of any memory encryption solution is the fact that, unlike the hard disk where data is sequentially stored for access, memory is used in a broad variety of dynamic access patterns. Numerous decisions must be made concerning the granularity of encryption in operating systems. For example, a running program will utilize RAM during execution for both stacks and heap space. The stack is accessed so frequently that adding encryption/decryption overhead to stack operations might prove prohibitive. Unfortunately, during context switches, registers containing sensitive information are normally saved to the stack in external memory. Additionally, the heap size, for any given program, is not normally known a-priori. The complexities of memory mapped input-output peripherals result in an inability to cache mapped regions. This naturally presents a challenge, if the overarching concept involves decrypting memory only after it is brought onto to the processor chip. It is not clear if the entire memory should be encrypted with a single key, or if shared libraries, individual programs, and/or

data should be encrypted independently using separate keys. Alternatively should individual functions or cache blocks be used as the unit of encryption? All of these decisions incur a tradeoff between the number of keys that must be securely stored, versus the degree of protection and overlapping in operations that can be realized.

The literature on memory encryption is largely concerned with three core approaches based on hardware enhancements, operating system enhancements, and specialized industrial applications. These approaches are explored in the sections that follow. Unfortunately, almost all of the hardware and operating system enhancements have only been implemented through simulation or emulation, and as a result, the claims have yet to be validated and quantified on practical systems.

#### **2.2 Monolithic Processor Enhancements**

The general scope of hardware enhancements includes a number of approaches that have added specialized encryption units and/or key storage mechanisms to existing processor designs. In addition, several efforts have proposed inserting hardware into the system bus to leverage legacy code and hardware. Although the first patents detailing memory encryption were executed in 1979 [Best 1979; Best 1981; Best 1984], and the first paper detailing their use was published in 1980 [Best 1980], the body of in-depth academic research related to general-purpose memory encryption has occurred primarily in the past decade.

One of the earliest papers, often referenced by others of this genre, highlights an execute-only memory (XOM) architecture [Lie et al. 2000]. This architecture was designed to combat software piracy and combines aspects of both public and symmetric key encryption. Public key encryption is used to deliver binary code to the XOM chip,

which maintains a unique private key. This allows vendors to encrypt the code for a particular system and ensures that it cannot be reused on another system. The header associated with the code includes a symmetric key embedded within it, which is used to segment memory into unique compartments at the granularity of a process. In order to map compartments to encryption keys, each compartment is tagged. A single null compartment is created to hold all unencrypted processes and libraries. This compartment enables communication between encrypted processes while allowing all processes to use shared libraries.

The XOM architecture assumes several hardware enhancements to existing processors. Special microcode is required to store the unique private key in a private onchip memory. A symmetric-key encryption unit is added to the processor, together with a special privileged mode of operation for encryption. A hardware trap on instruction cache misses provides a segue into this encryption mode for encrypted code. When a cache miss occurs, the instruction is decrypted before being loaded into the processors instruction register. Although the authors state encryption could be accomplished in software they acknowledge that this would be very expensive in terms of overhead. Since many of the papers that follow XOM include similar hardware, only the differences or unique contributions of the other systems will be discussed.

XOM encrypts memory in a straightforward manner commonly known by the encryption community as *electronic codebook mode* but referred to in the literature as *direct encryption*. Each code block is decrypted by the encryption unit after it is read from memory, and encrypted before it is written back to memory. Kgil et al. [2005] propose an additional chip enhancement targeted at improving the security of direct

encryption, called ChipLock. This involves storing a small trusted part of an operating system kernel, called TrustCode, in a read-only memory (ROM), termed TrustROM. Additional instructions are added to enable secure communication between the trusted and untrusted parts of the operating system. The TrustCode intercepts all system calls for memory access and performs encryption without the knowledge of the untrusted portion of the operating system. Symmetric keys are assigned at the granularity of the process as in XOM, with additional keys for shared libraries and the concept of a null bit for applications that are not encrypted.

Rogers et al. [2005] attempt to improve on direct encryption using an alternative mechanism, *prefetching*. Prefetching uses stream buffers to capture *spatial locality* in programs by copying additional contiguous blocks of memory into local cache after each miss. These buffers are especially good at speeding up programs that exhibit *spatial locality* and *contiguous access*, such as scientific applications [Hennessy et al. 2006]. An alternative prefetching technique that involves correlation tables to capture and reuse *temporal locality*, i.e. complex and/or non-contiguous sequences of memory access, is also used.

In another direct encryption scheme, Hong et al. [2011] perform a tradeoff analysis on the use of sensitive (encrypted) versus frequently accessed (unencrypted) data in embedded scratch pad memories (SPM). SPM's are software controlled SRAMs, as opposed to caches, which are typically controlled by hardware. There are numerous papers that discuss both static and dynamic policies for SPM utilization to reduce power consumption and memory access latency. DynaPoMP was the first to consider partitioning the SPM into distinct areas with an area dedicated to sensitive code and data.

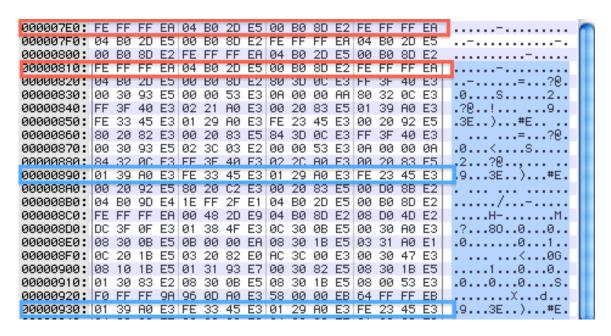

The authors vary the size of the two partitions in an attempt to find the most efficient ratio. There is a common assumption that an encryption unit and special instructions are available in hardware. Unfortunately, direct encryption schemes involve a one-to-one mapping between blocks of unencrypted and encrypted code. As a result, encrypted code portrays a similar statistical distribution as the unencrypted code, thus allowing a significant amount of information to be gleaned from frequency analysis [Chhabra 2010]. Based on the typical AES encryption block size of 128 bits, programs tend to exhibit multiple redundancies that would lead to information leakage as shown in Figure 2.

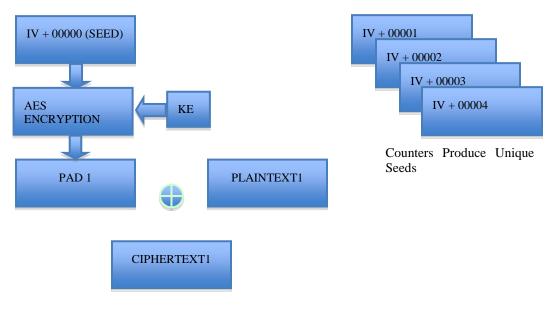

After XOM, a number of papers attempt to mitigate this statistical weakness using a one-time pad (OTP) [Suh et al. 2003; Shi et al. 2004; Yang et al. 2005; Yan et al. 2006; Suh et al. 2007; Duc et al. 2006]. A traditional OTP is simply a source of random data that is used exactly once to encrypt a particular communication. This is a form of symmetric-key cryptography since both the sender and receiver require the pad. Although variously referred to as "pseudo one time pads" (POTP) in the literature, this is more commonly known in the encryption community as counter-mode (CTR) encryption. In computing, OTP's are created by encrypting a unique seed, typically producing a pad of 128 bits in length (i.e. the size of an AES encryption block) as shown in Figure 3. A fixed initialization vector (Nonce) is concatenated with a counter producing a unique The seed is encrypted with a unique key generating the pad, which is then exclusively or'ed (XOR) with the plaintext to produce the cipher text. In memory encryption schemes, the counter is stored either internally, in a cached table that maps to a memory address, or unencrypted within the encrypted memory itself (i.e. RAM) since counter secrecy is not required [Yan et al. 2006]. When a memory reference occurs, the

pad is regenerated, using the counter (and optionally some other component such as the virtual address) and initialization vector, then exclusively or'ed with the encrypted data to produce the original plaintext. Since the encryption operation is no longer dependent upon the data in memory, this regeneration can be overlapped with the memory read, decreasing the performance impact of decryption.

Figure 2: Redundancies in 128-Bit Sections of Binary Code

Figure 3: Pseudo One-Time Pad or Counter Mode Encryption

Aegis is a OTP approach that was originally proposed as a direct encryption scheme in 2003. Suh et al. propose the one-time pad approach in [2003b], perhaps illustrating the shift away from direct encryption in the community. One interesting contribution from this paper is the method of creating the unique key. The chip-specific encryption key is created by *physically unclonable functions* (PUF) [Suh et al. 2003a]. These functions make use of unique timing characteristics of "identical" models of the hardware to create the unique keys. Aegis is one of several approaches that include the idea of a small, protected security kernel that is separate from the rest of the untrusted operating system. Unfortunately, this kernel measures 74K lines of code for virtual memory management alone [Chhabra et al. 2011].

In Yang et al. [2005], the authors look to reduce the execution overhead of using one-time pads by adding a *sequence number cache* (SNC) onto the chip below the L2 cache. Sequence numbers, in this paper, correspond to the counters used in Figure 3. However, the initialization vector is unique per cache block and corresponds to the virtual address. Since the addresses are unique across memory, the pads (and thus the ciphertext) will be *spatially* unique. The counters are updated upon each write to memory ensuring *temporal* uniqueness (i.e. pads used for a single location will not be the same over time). The authors suggest that a reasonable addition to a chip would be a SNC of 64 KB. Based on this limitation, two policies for using the SNC are described. In the first policy, only the portion of memory corresponding to the number of available sequence numbers stored in the SNC can be encrypted. The amount of protected memory is therefore limited by the SNC size. In the second policy, additional memory lines are encrypted and sequence numbers that do not fit in the cache are stored in plaintext in

memory. Level two cache is increased in both methods by 4% in order to store the virtual memory addresses used to index into the SNC since only physical addresses are typically available above the level one cache.

In [2006], Yan et al. present *split counter mode* encryption, in which they introduce major and minor page counters. In this scheme, a 4 KB page has one 64 bit major counter and 64 7-bit minor counters (one per 64 Byte cache line). Concatenating the page major counter with the cache line minor counter forms the overall counter. This counter is further concatenated with the memory block's virtual address, and an initialization vector to form the unique seed. The vector can be unique per process, group of processes or system based on security requirements.

In CryptoPage [Duc et al. 2006], the authors again attempt to enhance the OTP encryption scheme. In this case, they modify the translation look-aside buffer (TLB) and page table structures, adding information for pad computation. Since the TLB and/or page table structures are always accessed before a memory read, the authors claim that the pad generation latency can be almost completely removed. This scheme is implemented on top of the *HIDE* memory obfuscation technique whereby access patterns are permuted in memory at designated times [Zhuang et al. 2004].

In *address independent seed encryption* (AISE) [Rogers et al. 2007], the authors propose to use a *logical* identifier, rather than the virtual or physical block address, as the major counter portion of the seed. This scheme closely resembles split mode counters [Yan et al. 2006]. It is claimed that using an address independent seed enables common memory management techniques, such as virtual addressing, paging, and inter-process sharing. In [2011], Chhabra et al. propose to build a secure hypervisor upon the AISE

substrate. The hypervisor implements *memory cloaking*, whereby the operating system only has access to the encrypted pages of applications. The authors suggest that this cloaking will protect processes from vulnerabilities in the insecure underlying operating system, with an order of magnitude fewer lines of code than in Aegis.

In [2007], Nagarajan et al. propose compiler-assisted memory encryption for embedded processors assuming some limited hardware support. They claim that the current counter mode solutions require too much silicon space for small and medium size embedded processors. The compiler supports memory encryption by introducing special instructions to calculate OTP's prior to loads and stores, and assumes the existence of additional process-unique registers used to store the counters. Space for the unique key and global counter is also provided inside the CPU and the availability of a crypto unit is assumed. The compiler attempts to ensure that the counter used for a store is still available for successive loads from the same memory location. A global counter must be available for those loads and stores that do not match one of the process-unique counter registers. The authors claim that since frequently executed loads and stores exhibit highly accurate counter matching, 8 special hardware registers with 32 counters are sufficient for reasonable performance.

#### 2.3 Multi-Processor Enhancements

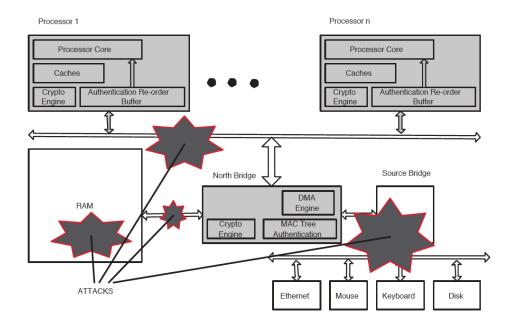

Chhabra et al. [2010] compare a symmetric multiprocessor (SMP) and a distributed shared memory (DSM) design; they also provide a quick look at monolithic memory encryption. Whereas the efficiency of memory-to-cache confidentiality is the primary concern for monolithic processors, multiprocessor systems must also protect cache-to-cache traffic. In symmetric multiprocessors, the shared bus between caches and

memory can be used as a way to coordinate messages between processors. This sharing is not available in distributed shared memory systems, which must use message passing. Additionally, DSM systems can be observed more easily than monolithic chips via interconnect wires that are exposed at the back of server racks [Rogers et al. 2008].

In [2004], Shi et al. use OTP encryption both for memory-to-cache and cache-to-cache transfers as shown in Figure 4. In this approach sequence numbers (counters) are incremented in lockstep in each separate processor resulting in a claim of "very low" overhead for cache-to-cache encryption. A hardware mechanism in the processors ensures that the sequence numbers begin differently after each reboot. Besides the typical crypto-engines placed within each processor core, a separate crypto-unit is embedded in the north bridge memory controller for memory-to-cache transfers. For these transfers, 64-bit sequence numbers are stored in RAM reducing the available memory by 25 percent.

Figure 4: SMP Architecture with Memory Encryption Engine

In SENSS [2005], Zhang et al. utilize OTP's for memory-to-cache transfers and AES cipher block-chaining mode for cache-to-cache transfers. This alternative to direct encryption divides the clear text into blocks and encrypts the first block with an initialization vector; subsequent blocks are chained together such that the output of the previous block is XOR'd with the input of the next before being encrypted. Cipher block chaining implies sequential access since each block depends upon each previous block. RAM is typically accessed in a fairly random pattern, so this mode of operation is impractical except on a very small scale (per cache block for example). Cipher block chaining is acceptable for cache-to-cache transfers as only one previous encrypted block must be stored at each processor (i.e. there is no requirement for access to previously encrypted blocks). The authors propose a secure hardware unit (SHU), located at each processor, comprising an encryption unit with associated storage for keeping track of communication. This storage includes memory for a group processor matrix and group information table. The group processor matrix is used by each SHU to determine if broadcast messages should be read. The matrix is only 640 bytes in size, assuming a maximum of 32 processors. The information table contains the secret information for communicating between groups, such as the symmetric key and pads, and is estimated at 149 KB. An additional 11 bus lines are used for control signals and to pass group id numbers. In Jannepally et al. [2009], the SENSS scheme is improved using Galois Counter-Mode (GCM) AES, which provides both encryption and authentication simultaneously.

In I2SEMS [2007], Lee et al. create a scheme that is claimed to be applicable to both SMP and DSM systems. They propose a global counter cache (GCC) that assigns

different sections of the overall counter space to processors (akin to assigning blocks of IP addresses to groups of computers). The blocks of counters are also broadcast to all processors so that they can begin pre-computation of pads. Each processor has a keystream (pad) queue, keystream cache and keystream pool. The queue and cache both contain pads for encryption. The queue has new pads while the cache contains pads that have been used previously. The authors claim that pads may be reused as long as the plaintext has not been modified and that their scheme scales well to large numbers of processors since over 25% of pads are reused. The keystream pool holds pads for incoming data. The pads are chosen based on prediction with the aid of the broadcast scheme.

The first paper to exclusively address DSM systems [2006] was by Rogers et al., who again make use of counter mode encryption. Since the memory-to-cache scheme is similar to those already discussed, we only focus on the cache-to-cache scheme. The authors propose three methods for managing the pad counters: *private, shared,* and *cached* counter stream. In the first *private* method, tables are kept within each processor with separate counters for send and receive operations to/from every other processor in the system. While this technique allows for nearly perfect pad hit rates, and therefore very low overhead, it suffers from large storage needs (180KB in each processor for a 1024-processor DSM). The second *shared* scheme, aims to reduce the storage requirement by eliminating half of the table: Instead of keeping track of send counters for each processor, only one counter is kept for sending pads. This results in increased execution overhead since messages are less likely to arrive contiguously and therefore must be recomputed. The final *cached* scheme takes advantage of the intuition that

processors in DSM systems often communicate in cliques [Lee et al. 2007]. The overall table size is thus reduced to a quarter of the private scheme's memory with minimal impact on execution overhead. In a subsequent paper [2008], Rogers et al. identify the previous scheme as a two level approach since remote memory requests will first be decrypted by the owning processor and then re-encrypted for cache-to-cache transmission to another processor. In the new scheme, a single mechanism is used for both memory-to-cache and cache-to-cache transfers bypassing the unnecessary decryption and re-encryption. The associated hardware includes a 32-entry buffer (1 KB) for counter prediction and a 32-entry mask buffer that stores a bit vector of recent data block accesses (512 bytes).

#### 2.4 Bus Inserts

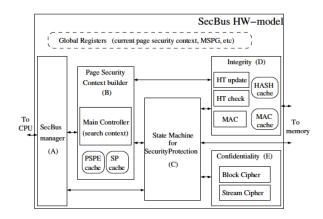

Another area of active research involves placing specialized encryption hardware outside of the CPU. The locations include the memory bus (i.e. externally between system memory and the CPU) and within RAM. The primary goal of this approach is to increase the likelihood that this solution will be adopted since re-engineering of commodity processors is not required. One such approach, SecBus [Su et al. 2009] shown in Figure 5, can be located at the frontend of the memory controller. The authors state that this method of modification is required in many user markets when embedding new functionality into systems with legacy CPUs. SecBus is essentially a cryptographic coprocessor with internal storage and bus manager. The page security parameters entry (PSPE) includes information to map pages to corresponding security policy (SP), which includes a confidentiality mode, integrity mode and secret key. SecBus includes the

ability to choose between multiple encryption modes based on the type of memory (i.e. code or data).

Figure 5: SecBus Hardware Augmentation Model

In [2008], Enck et al. design a memory encryption control unit (MECU) to again be placed on the memory bus between the processor and RAM. The goal of MECU is to provide the same guarantees of security provided by the volatility of traditional RAM when utilizing non-volatile main memory. MECU uses a OTP scheme with internal storage for the array of counter seeds and the encryption engine. A secret key and master counter, which tracks the greatest overall counter, are stored on a removable smart card. In order to reduce the storage requirement, the encryption chunk granularity is increased from one cache line to n, where n is 256 in the common case but can grow to the entire memory for experimentation.

With the same goal as [Enck et al. 2008], Chhabra et al. [2011] propose placing the cryptographic engine and other required hardware in non-volatile RAM modules. Their scheme keeps most of the RAM encrypted with a smaller group of frequently accessed pages in plaintext in a similar fashion to [Hong et al. 2011]. The authors claim

that by doing this, the remainder of the RAM can be encrypted at power-down within 5 seconds, paralleling traditional RAM volatility.

## 2.5 Operating System Enhancements

Similar to the bus insert method for enabling memory encryption, software-only approaches seek to provide solutions that can be implemented without major changes to applications or commodity hardware to increase the likelihood of adoption.

In [2008], Chen et al. propose an operating system controlled memory bus encryption technique for systems that offer scratch pad memory (SPM) or cache locking that is software controllable. Both types of memory are available in some embedded processors including the Intel XScale series. A new symmetric key is generated each time the system is booted and random vectors (32 bits generated using /dev/urandom and padded with 0's) are used to initialize AES encryption at the granularity of a page. The vectors are then placed in memory with the pages. This scheme requires a 0.4% space overhead when used with 1 KB pages. When a page fault occurs for a secure process, a specially crafted handler moves the encrypted page into the chip boundary and decrypts it there placing it into the cache, which is then locked to prevent leakage of sensitive data. The locked region holds several pages of data and encryption variables. In order to facilitate this special handling, a Boolean status variable is added to each process descriptor residing in kernel address space. The authors note the scheme is appropriate when embedded systems designers can tolerate a significant performance overhead for protected processes.

In Cryptkeeper [2010], Peterson modifies the virtual memory manager and partitions RAM into two parts; the plaintext *Clear* and the encrypted *Crypt*. Essentially,

this technique aims to reduce the amount of sensitive data available at any time in memory. All pages initially start in the clear and the number of Free Clear Pages (FCP) is reduced with each allocation. The least recently used pages are encrypted and moved to the Crypt when the limit of FCP runs low. This operates under the assumption that the number of high use pages will be small, and therefore most infrequently used pages will be encrypted. This has the unfortunate side effect of maintaining all the important pages in the clear. A prototype Cryptkeeper system was designed based on the Linux 2.6.24 kernel. The kernel page structure was extended to include information indicating whether a page is in the Clear or Crypt portions of memory.

## 2.6 Specialized Industrial Devices

Industry offers several solutions for memory encryption including low frequency specialized processors for ATM use, expensive tamper resistant coprocessors for financial transactions, proprietary gaming systems and, more recently, adding technologies in commodity processors that enhance trust.

The Dallas Semiconductor 5002FP secure processor is an 8051 compliant processor and runs at a maximum frequency of 16 MHz [Dallas 1997]. The processor encrypts memory addresses to prevent traffic analysis on the memory bus in addition to data. The device uses spare processor cycles to place dummy memory accesses on the bus since analysis of memory access patterns can reveal useful information (e.g. encryption keys or sensitive algorithms) to attackers [Gao et al. 2006]. All external memory is encrypted via a proprietary encryption algorithm with a 64-bit secret key that is stored in a tamper-protected, battery-maintained static RAM. Plaintext code is

uploaded via serial port and a firmware monitor encrypts it and stores it in external RAM. The 5002FP is commonly used in credit card (i.e. point of sale) terminals, automated teller machines, and pay-TV decoders [Yang et al. 2005]. A newer version (DS5250) includes a larger 1 KB instruction cache, which, according to Dallas Semiconductor, reduces the effect of memory encryption on execution speed providing a 2.5X performance improvement. The newer processor runs at a maximum frequency of 25 MHz.

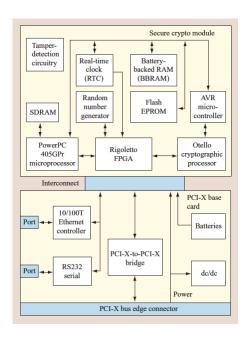

Another active area of secure hardware used in industry is the cryptographic coprocessor such as the IBM PCI-4758. These coprocessors include an impressive array of technology including a secure processing environment, microprocessor, custom encryption and random number generation hardware, and shields and sensors (to help protect against destructive attacks) [Howgrave-Graham et al. 2001]. However, they are generally limited to IBM server platforms under customized contracts and tend to be used for financial and banking systems. A modified version of CP/Q message-passing kernel runs on the system providing a subset of typical features. The secure module is encased in a flexible mesh of overlapping conductive lines meant to prevent any physical intrusion. If such intrusion is detected the system responds by zeroizing the internal RAM which holds the secret key. The stated purpose of the IBM secure coprocessor is to offload computationally intensive cryptographic processes (e.g. specialized financial transactions) from the host server.

While mostly constrained for use in playing games and other entertainment media (unless compromised) gaming systems are some of the most capable (e.g. fast processor speed and relatively large storage) to incorporate memory encryption techniques. As an

example of these systems, the Xbox 360 provides encrypted/signed bootup and executables, partially encrypted RAM, and an encrypted hypervisor [Steil and Domke 2008]. These mechanisms are provided via a Microsoft proprietary processor with 64 KB of internal RAM, random number generation and encryption as opposed to the "off the shelf" processor used in the original Xbox. While it is possible to use the Xbox as a general-purpose platform, this requires compromising the system's security measures first. Alternatively, the Sony Playstation 3 includes many of the same security mechanisms of the Xbox 360, but allows the end user to partition the hard drive for use with a chosen (e.g. Linux) operating system. However, the proprietary security mechanisms of the Playstation 3 are not available to the additional operating system [Conrad et al. 2010].

The trusted computing group (TCG) designed the Trusted Platform Module (TPM) based on the IBM 4758 secure coprocessor [Vandana 2008]. The TPM provides secure key storage and the capability for platform measurements for chain-of-trust booting. The current specification for the TPM calls for it to be attached to a typical motherboard via the low pin count (LPC) bus. The TPM provides non-volatile storage for encryption keys and an encryption engine including support for RSA, SHA-1 hashing, and random number generation. The LPC bus is limited in speed and the cryptographic engine on the TPM is not meant to be a cryptographic accelerator. Over 350 million TPMs were deployed as of 2010 and can be found in many laptops and general-purpose computers (disabled by default) [Dunn et al. 2011]. On its own, the TPM would not be powerful enough to provide general memory encryption with acceptable overhead. However, the TPM may be used to provide secure key storage between power cycles.

Unfortunately, a small weakness still exists in that keys must be sent in the clear over the LPC bus to the CPU, allowing a bus snooping attack to capture them [Simmons 2011]. Other interesting methods to store encryption keys have been described recently in schemes targeted at preventing cold-boot attacks on full disk encryption. For example, Muller et al. describe TRESOR, a technique for utilizing CPU debug registers for encryption key storage [2011]. In order to protect against memory attacks on the key, the decryption routines are carefully written in assembly to avoid using the stack, heap or data segment during decryption. By utilizing AES-NI, TRESOR was shown to perform better than software based full disk encryption (17.04 MB/s vs. 14.67 MB/s) with the additional protection. A similar approach is taken in [Simmons 2011] except that registers used for performance counting are targeted for master key storage with multiple encrypted keys being stored in RAM.

Intel has recently filed several patents for processors incorporating memory encryption, perhaps indicating a move toward support in commodity processors [Gueron 2012], [Gueron 2013]. The patents describe a new processor with hardware including a memory encryption engine (MEE) and on-chip storage for counters. The hardware described in the application modifies the AES-XTS *tweak* mode of operation. XTS stands for XEX based tweaked codebook mode with ciphertext stealing and this mode is typically used for disk encryption [Martin 2010]. A tweak is similar to an initialization vector and is an additional input to a cipher designed to protect against similarities in ciphertext. For disk encryption, the tweak tends to be the sector number. In Intel's patents, the tweak is extended to include a time stamp or counter value along with the memory address. The counter is updated each time a cache line is written, providing

protection against a replay attack where a chunk of memory is copied and inserted back into memory at a later time.

## 2.7 Commoditized Security Hardware

Most of the approaches in the ME literature assume that several components are necessary for secure, efficient performance: a way to generate and securely store encryption keys (i.e. not in RAM); and hardware to accelerate encryption performance. Although not targeted specifically at memory encryption, nascent technology could be used to form the basis of an encrypted memory solution for general-purpose systems. One of the developers of IBM's 4758 cryptographic coprocessor has suggested, for example, that a general-purpose system with hardware support (such as a trusted platform module) could theoretically be turned into a somewhat less secure but more pervasive and less expensive version of the 4758 [Smith 2004]. Encryption engines have been added to Intel's core i5 and i7, AMD's bulldozer and various embedded processors [Muller et al. 2011]. For X86 systems, Intel's advanced encryption standard - new instructions (AES-NI) include six instructions to speed up key expansion and encryption. Intel states that the new instructions can provide a two to three time performance improvement over software-only approaches for non-parallel modes of operation such as cipher-blockchaining (CBC) encryption [Gueron 2010]. Further, a 10-fold improvement can be realized for parallelizable modes including CBC-decrypt and counter-mode encryption (CTR). As an example of the performance improvement possibilities, the authors ran TrueCrypt's encryption algorithm benchmark test on a MacBook Pro with an Intel i7 dual-core, 2.66 GHz CPU. Using a 5 MB buffer in RAM, the throughput averages 202

MB/s without AES-NI support, and 1 GB/s with it, thus approaching the speed required to overcome encryption overheads on general-purpose systems.

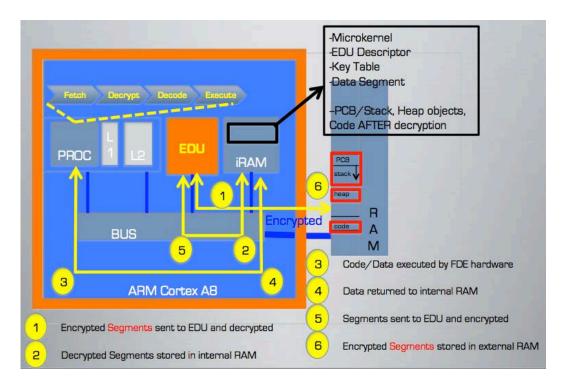

Henson and Taylor [2013] are among the first to take advantage of this commoditization of security hardware for use in implementing memory encryption. The IMX53 development board is used in conjunction with an ARM cortex A8 processor that contains security hardware within its boundary. The hardware consists of encryption and hashing engines and random number generation as well as facilities for trusted booting. A small (~35KB) microkernel called *Bear* is developed and integrated with the A8 and security hardware. As the work is implemented on commodity hardware, it considers many of the details that are not thoroughly addressed in the other surveyed literature (i.e. simulation work). For example, encryption is explored at process component granularity (e.g. stack, heap, code) with analysis of the overhead for encrypting each component. The work takes advantage of on-chip, internal RAM (iRAM) as well as cache to provide the secure processing environment. Outside of this chip boundary, all code and data are encrypted. Most of the ME functionality is tied to the context switching routines in the microkernel. The microkernel fits into the iRAM and is part of the TCB in this work.

## 2.8 Analysis

Although the primary goal of memory encryption architectures is security, the work tends to focus on the overheads involved, both in chip area and performance degradation. This is unfortunate though unsurprising given that most of the work is simulated and it is within the intricacies of implementation that security vulnerabilities tend to be found. The analysis here focuses on the data available including encryption latencies, performance degradation, simulation environments, operating system

assumptions, overall space requirements, user requirements and general observations regarding security.

Since the performance degradation of memory encryption results in less likelihood of its use, it is an extremely important factor in the comparison of different schemes. One of the major issues with the body of literature is the lack of a common set of measurement standards, with explicit assumptions regarding memory access latency, encryption latency etc. This makes it difficult to directly compare approaches and draw valid conclusions. Encryption latencies are typically given as the number of cycles required to encrypt/decrypt a cache line that varies from 16 to 128 bytes, typically using a value of 64 bytes. The latencies range from 11 to 160 cycles with 80 being the most common value (especially in the multiprocessor work). The authors in [Rogers et al. 2006] state that 80-cycle latency is assumed in order not to penalize the direct encryption scheme (upon which they are trying to improve) since a recent (circa 2006) hardware implementation required over 300 ns. Cycles and nanoseconds are often used interchangeably since many of the systems modeled are based on 1 GHz processors. Low encryption latencies are possible but at the cost of large die area making them appropriate for powerful processors. For example, it is claimed in [Suh et al. 2003] that 40 cycle-latency is achievable with four AES units chained together requiring 300,000 gates. In AEGIS [Suh et al. 2007], a single AES unit is estimated at 86,655 gates, which the authors claim is modest when compared to the size of commercial cores. Unfortunately, the OR1200 soft core used to demonstrate Aegis is only approximately 60,000 gates (meaning one AES unit is 144% of the original core size).

The methods used for determining performance include mathematical models, simulation, kernel prototypes and FPGA prototypes with various benchmarking suites used in the latter three. Simulation is performed with (in order of decreasing usage) SimpleScalar, Simics, SESC, GEMS, SOC designer, RSIM, and M5. Benchmark suites used include SPEC2000, SPLASH2, Mediabench, EEMBC and several user developed varieties such as one entitled "memeater". A group of the simulations utilize SimpleScalar and [Duc and Keyell 2006] notes that this simulator neglects the impact of the operating system and other running processes. Besides these limitations, some authors admit a lack of model fidelity with significant differences between systems modeled and those targeted. For example, in [Chen et al. 2008] an x86 architecture is modeled since it happens to be better supported by the simulation tool (Simics) even though the scheme is actually targeted for embedded-ARM systems. Unfortunately, even if a system under test were to be modeled perfectly, the simulation tools themselves have been shown to sometimes exhibit behavior unlike real systems. In [Muller et al. 2011], the behavior of CPU registers is interrogated under simulation in QEMU with the contents surviving soft-boot. Such behavior would circumvent the protections afforded in that work, however, real hardware behaves differently and zeroes out the registers.

A summary of the featured techniques is presented in Table I to provide an overview of memory encryption. The table includes basic characteristics of each approach such as complexity information including execution and storage overheads. In order to fairly compare the different schemes, several assumptions were made. For example, the size of internal storage required is sometimes dependent on the size of RAM, and where possible an assumption of 1 GB is made. Similarly, an assumption of

32 processors is made where possible for the multiprocessor approaches. When there is no data available, an element of the table is left blank. Two values are commonly reported in the literature with regard to execution overhead: worst case (max) and the average (based on some suite of benchmark tests) percentage slowdown when compared to non-protected execution. Storage overheads typically break down into internal (cache) and external (RAM) usage (and one example of the increase to overall code size). Operating system approach indicates whether the authors assumed the existence of a secure kernel (A), described hardware to protect the processes from an insecure kernel (H), or ignored the operating system (I) (further discussion of this requirement below). Finally, slightly fewer than two-thirds of the authors included memory integrity (I) along with memory confidentiality (C) mechanisms. Where possible, results (e.g. execution overhead and storage) are provided for memory encryption only. Maturity indicates how the technique was evaluated if not a commercial product. Methods appear in the table as they are presented in the survey and detailed in the approach column: monolithic processor, multiprocessor, bus insert, or software/direct or counter mode encryption. Security level refers to the overall security of the ME approach with the following factors from the table taken into consideration: category, operating system approach, encryption algorithm, and partial vs. full ME. Specifically, the five sections are scored with maximum points as follows: category (1), operating system approach (2), encryption algorithm (2), and encryption level (1). A score of 6 represents a system capable of addressing a wider range of memory threats than those with lower scores. For category, no points are given for bus inserts and software approaches due to inherent weaknesses of these techniques when compared to hardware approaches. The operating system